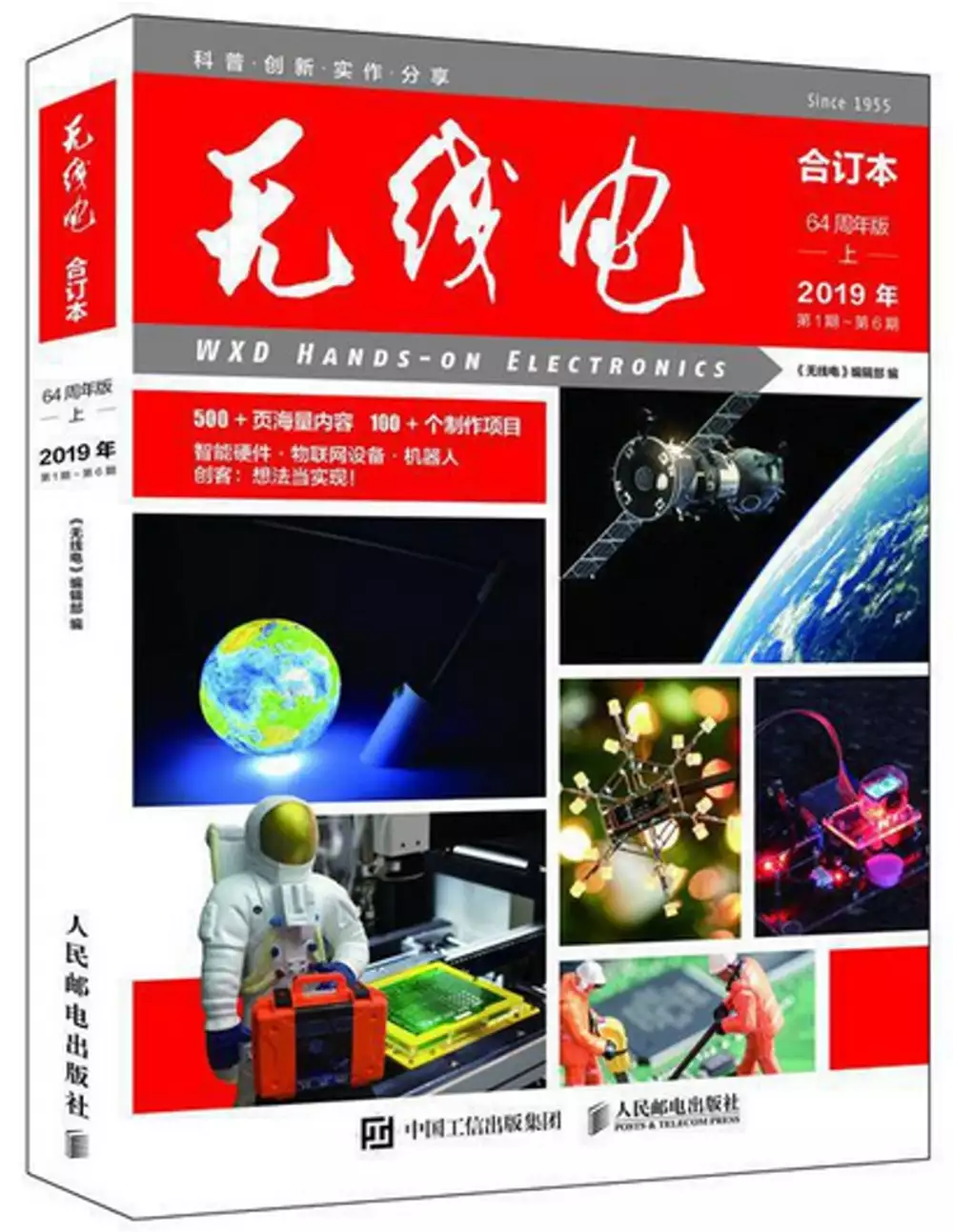

資料路徑的問題,我們搜遍了碩博士論文和台灣出版的書籍,推薦《無線電》編輯部寫的 無線電合訂本(64周年版上)(2019年第1期-第6期) 和何賓的 Xilinx Zynq-7000嵌入式系統設計與實現:基於Arm Cortex-A9雙核處理器和Vivado的設計方法(第二版)都 可以從中找到所需的評價。

另外網站Microsoft Store 版本App 的資料儲存 - Heresy's Space也說明:安裝路徑. Program Files. Windows 最典型的應用程式安裝路徑,以現在都是x64 的電腦來說,基本上就是:.

這兩本書分別來自人民郵電出版社 和電子工業所出版 。

國立中正大學 電機工程研究所 黃崇勛所指導 陳威仁的 以時序錯誤導向電軌調變技術實現之細緻化電壓調節及其於能耗可調數位系統之應用 (2021),提出資料路徑關鍵因素是什麼,來自於數位控制低壓降線性穩壓器、可容錯數位系統、即時視訊處理、電源軌抖動、電壓調節技術。

而第二篇論文國立中山大學 資訊工程學系研究所 鄺獻榮所指導 鍾明學的 深度神經網路硬體加速器之資料路徑生成器設計與實作 (2021),提出因為有 深度學習、神經網路、硬體加速器、通用資料路徑、資料路徑生成器的重點而找出了 資料路徑的解答。

最後網站颱風消息| 交通部中央氣象局則補充:路徑 潛勢預測圖的目的在表示颱風中心未來可能移入的範圍。 ... 本產品為機率預報圖之一種,係將最新的颱風預測資料以及過去預測誤差的統計特性綜合而成。

無線電合訂本(64周年版上)(2019年第1期-第6期)

為了解決資料路徑 的問題,作者《無線電》編輯部 這樣論述:

《〈無線電〉合訂本(64周年版·上)》囊括了《無線電》雜誌2019年第1~6期所有欄目的全部內容,包含專題以及創客、製作、裝備、火腿、入門、教育、史話等欄目的所有文章,其中有熱門的開源硬體、智慧控制、物聯網應用、機器人製作、人工智慧應用等內容,也有經典的電路設計、電學基礎知識等內容,還有豐富的創客活動與創客空間的相關資訊。這些文章經過整理,按欄目、期號等重新分類編排,以方便讀者閱讀。與部分文章相關的來源程式、印製電路板圖等資料請到目錄所示的下載平臺下載。 本書內容豐富,涉及電子技術廣泛,文章精練,實用性強,適合廣大電子愛好者、電子技術人員、創客及相關專業師生閱讀。 《無線

電》於1955年創刊,是國內電子及無線電通信類報刊中創刊最早、發行量最大的知名科普雜誌,累計發行量超過3億冊,現為國內發行量最大的創客實體雜誌,曾獲“國家期刊獎”、“公眾喜愛的科普期刊”稱號。 《無線電》雜誌堅持“科普創新實踐 分享”的理念,為讀者提供涵蓋創客空間介紹、創意製作專案、電子科普知識、工具儀錶資訊、創科教育動態、電子技術前沿資訊及行業活動資訊等豐富的內容。 專題 SPECIAL 科學家為什麼一直造衛星——專訪天儀星空設計師 天儀小姐姐(002) 衛星天線上為什麼會有刻度? 陳險峰(005) 不僅要上天 還要去探月 ——哈工大微衛星團體解讀“龍江二號” 黃家和

(009) 我,立方星 吳靜 邱寶貴 餘靜 陳斌 李亮(012) 創客 MAKER WINDLOOM織風——用Arduino的音樂“織”出鄉愁與思念 李思曼(013) 探訪鄧稼先、阿姆斯壯母校——普渡大學Bechtel創新設計中心 參觀隨感 狄勇 錢昭媛(016) 格鬥機器人Longbility建造日誌 李玉傑(021) 桌上彩虹 金煜人 劉銘(024) 造一個鋼鐵俠的MK6方舟反應堆 dinochen(026) POV版美國隊長盾牌 dinochen(028) 雷神之錘無線充電藍牙音箱 陳傑(030) 製作 PROJECT 轉鼓型迷你格鬥機器人鐵角龍建造日誌 鄧斌華(032) 用雷射雷達製作

察打一體自動化火炮模型 周瑜(038) 製作遊戲搖杆—電路設計與軟體程式設計篇 張彬傑(042) 設計可探測隱蔽電子產品的非線性結點探測器 劉虎(BD8AAA)沈昊宸(BH1THG)(047) 直流信號多功能隔離模組 趙明(051) 給手機增加一雙鐳射測距“眼睛” 楊潤靖(054) 暖心Baymax為你奏曲 —多功能大白呼吸燈雙聲道音箱 丁涵高深(057) 為7英寸LCD觸控式螢幕做一個soulmate 王立(061) DIY個人專屬微型FM電臺 辛國民(062) 隨表情而動的兔子帽子 王立(064) 自動控制系統設計實例 球杆系統 饒廠長(067) “地球之光”小燈 王小明(073) 木質m

ini小鋼琴 李玲雪(076) 貼片式8×8×8全彩光立方 楊志雄(078) 用智慧手機製作可視門鈴 俞虹(080) 自製Makey Makey電子琴 徐廣淶(084) 定制自己的表情包顯示器 李一楠(086) 單車騎行安全提示裝備 張千一 陳傑(088) 用STM32和W5500實現AirPlay音訊播放 常席正 魏文龍(090) 程式控制恒流源 黃運發(097) 純手工焊接觸控式LED雪花 吳琪琦(100) 常用語盒子PHRASE BOX 王立(104) 多功能桌面時鐘 楊潤靖 金延平(106) 以板為軀的微型循跡避障遙控小車 丁涵高深(110) Arduino Leonardo自帶的“顯

示幕” 王岩柏(113) 基於STM32的PC音量控制器 溫正偉(116) 用三極管製作555時基電路 俞虹(119) 用萬用電路板製作RS-485通信自動換向電路 梁磊磊(121) 240W高功率密度、高效率LLC電源 餘勇(123) 用Arduino Pro Micro製作USB耳機轉接器 王岩柏(130) 製作數控電梯模型(上) 丁涵高深(133) 散發愛的光輝 ——基於IV-22螢光管的情人節硬核表白神器 狄勇(136) 物聯網氣象站 陳傑 李岩(139) 智能騎行安全帽 梁立昊 陳眾賢(143) 校園語音瀏覽機器人 孫浚銘 餘國罡(147) STM32指紋識別U盤 楊潤靖 宋彥濤(1

49) 汽車蓄電池虧電報警器 王樂揚(151) 製作心形藍牙音箱 楊潤靖(153) 用鐳射切割機DIY一台Arduino留聲機 章明幹(156) 用FPGA設計數位頻率計 於皓川(158) 製作數控電梯模型(下) 丁涵高深(163) 製作一體式控溫設備 李一楠(168) 智能Wi- Fi插排 於子明(170) 製作6P3P超線性推挽功率放大器 趙治湘(173) 腕式即時心率計 王岩柏(178) 自帶時鐘功能的大本鐘模型 陳傑 李岩(180) 使用MicroPython開發ESP8266 梁磊磊(182) DIY智能焊接吸煙儀 楊潤靖(185) 用DS3231製作自動控制亮度的4位元數碼管時鐘

辛國民(188) 用Arduino製作《推箱子》遊戲 賴浩文(191) DIY無負反饋三極管小功放 jupeter(198) 裝備 EQUIPMENT 直流穩壓可調電源必學使用技巧 楊法(BD4AAF)(201) 數位存儲示波器必學使用技巧 楊法(BD4AAF)(205) 頻率計必學使用技巧 楊法(BD4AAF)(209) 射頻功率計必學使用技巧 楊法(BD4AAF)(212) 數位存儲示波器必學測量技巧 楊法(BD4AAF)(216) 信號發生器必學使用技巧 楊法(BD4AAF)(220) 火腿 AMATEUR RADIO 2018年業餘無線電臺設備大盤點 聆聽(224) 為YAESU FT

-80C電臺製作專用資料盒 陳鐵石(BA2BA) 崔慶海(BD2CO) 宋琦(BG2AQJ)(231) 手持接收機新銳——ICOM IC-R30使用測評 聆聽(234) 數字對講機百家爭鳴(上) ——歐訊新款DMR數字對講機 聆聽(237) 數字對講機百家爭鳴(下) ——歐訊新款DMR數字對講機KG-UVN1測評 聆聽(240) 國產業餘無線電車載對講機再進化 ——歐訊KG-UV980P使用測評 聆聽(243) 入門 START WITH 寫給初學者的FPGA 入門指南(7) CPU架構基礎知識 張文挺(247) 快速開發智慧家居系統(1) 打開/關閉電燈的Hello World小程式 徐瑋(

250) 國產免費PCB 畫圖軟體立創EDA 從入門到實踐 入門篇 用立創EDA快速完成電路設計 郝以鵬(256) 開關電源設計(序) 開關電源行業現狀簡介 沈潔(258) 寫給初學者的FPGA 入門指南(8) 如何實現一個簡易CPU 張文挺(262) 開關電源設計(1) 開關電源的選型 沈潔(267) 國產免費PCB 畫圖軟體立創EDA 從入門到實踐 實戰篇 TP4056單節鋰電池充電器設計 郝以鵬(270) 快速開發智慧家居系統(2) 全面解析智慧控制盒的通信協議 徐瑋(274) 電子設備原型設計與實踐(1) 原型製作基礎 孫德慶(277) 電子設備原型設計與實踐(2) LED基礎知識 孫

德慶(282) 寫給初學者的FPGA 入門指南(9) 初步實現CPU模型 張文挺(288) 開關電源設計(2) 開關電源元器件的選型 沈潔(292) 快速開發智慧家居系統(3) 通過Internet遠端控制及訪問智慧控制盒 徐瑋(298) STM32 入門100 步(第8 步) 程式設計語言介紹 杜洋 洋桃電子(300) 國產免費PCB 畫圖軟體立創EDA 從入門到實踐 進階篇 使用立創EDA幫你提高電子設計效率 郝以鵬(304) CAD建模,SolidWorks和PDMS哪個更好用? 俞鈞楠(306) 電子設備原型設計與實踐(3) LED應用進階 孫德慶(309) 寫給初學者的FPGA 入門

指南(10) 實現簡易CPU模型資料路徑 張文挺(316) 開關電源設計(3) 開關電源變壓器的設計 沈潔(321) STM32 入門100 步(第9 步) C語言基礎知識(1) 杜洋 洋桃電子(330) 揭秘無線電(1) 身邊無處不在的無線電 楊偉峰 王楓(336) 快速開發智慧家居系統(4) 智慧家居燈光控制系統應用案例 徐瑋(340) 寫給初學者的FPGA 入門指南(11) 實現簡易CPU的控制單元 張文挺(345) 電子設備原型設計與實踐(4) PCB原理圖設計 孫德慶(350) 電路板生產過程大揭秘 徐瑋(360) 揭秘無線電(2) 無線電頻譜資源的巨大價值 楊偉峰 王楓(366)

開關電源設計(4) 開關電源的PCB設計 沈潔(368) STM32 入門100 步(第 10 步) C語言基礎知識(2) 杜洋 洋桃電子(372) 電子設備原型設計與實踐(5) PCB設計 孫德慶(378) 寫給初學者的FPGA 入門指南(12) 視頻輸出 張文挺(387) 快速開發智慧家居系統(5) DIY可遠端控制的智慧配電箱 徐瑋(391) 開關電源設計(5) 成本核算與總結 沈潔(397) STM32 入門100 步(第 11 步) C語言基礎知識(3) 杜洋 洋桃電子(402) 教育 EDUCATION 中國原創開源硬體——掌控板 為程式設計教育而生 周茂華(408) 製作“向日葵

”智能花盆 沈利彬(412) 用開源硬體學Python—解讀高中資訊技術新課標 宋順南(414) 用顏色識別感測器製作變色龍 章明幹(416) 製作燈光版猜拳機器人 亦承爸爸(418) 智能鑰匙忘帶提醒器 章明幹(420) 桌面空氣淨化器的設計與製作 南星(422) 可穿戴遙控式無人消防車模型 盧一鳴 李守良(424) 迷你兔雜訊提醒儀 康留元(426) 用Arduino和溫度感測器製作內能做功演示教具 王秀蓮(428) 手把手教你製作《祖瑪》遊戲手機殼 王文毅(430) 3D列印一台Arduino多功能智能檯燈 王世豪(432) 用micro:bit製作可穿戴的俯臥撐標準監測儀升級版 游慕曦

李守良(434) Arduino智慧升降電梯模型的設計與製作 沈睿怡 李守良(436) 楚風徐來——用掌控板製作宮廷電風扇 杜濤 王娜(438) DIY電容充放電演示儀 歐陽巨集志 歐陽宇軒(440) 用Arduino和舵機製作創新風向儀 任嘉暉 劉佳維 唐思源(441) 問與答 王德沅(443) 史話 HISTORY 收音機史話(五十二) 上海無線電四廠的電子管收音機(一) 陳漢燕 徐蜀(449) 20 世紀磁帶答錄機進化史(1) 答錄機的初始時代 田浩(453) 20 世紀磁帶答錄機進化史(2) 電子管開盤磁帶大型答錄機的發展 田浩(458) 收音機史話(五十三) 上海無線電四廠的電子管

收音機(二) 陳漢燕 徐蜀(464) 收音機史話(五十四) 上海無線電四廠的電子管收音機(三) 陳漢燕 徐蜀(468) 20 世紀磁帶答錄機進化史(3) 便攜化的開盤磁帶電子管答錄機 田浩(472) 20 世紀磁帶答錄機進化史(4) 便攜化的開盤磁帶電晶體答錄機 田浩(476) 收音機史話(五十五) 上海無線電四廠的晶體管收音機(一) 陳漢燕 徐蜀(480) 20 世紀磁帶答錄機進化史(5) 高端大型開盤磁帶答錄機 田浩(483) 收音機史話(五十六) 上海無線電四廠的晶體管收音機(二) 陳漢燕 徐蜀(488) 收音機史話(五十七) 上海無線電四廠的晶體管收音機(三) 陳漢燕 徐蜀(492)

20 世紀磁帶答錄機進化史(6) 臺式盒裝磁帶答錄機 田浩(496) 電子史:從紅色到白色,這一步,LED走了30年 馬懂煤(502)

資料路徑進入發燒排行的影片

TQC+Python基礎程式語言應用班第1次上課(環境設定與基本語法)

01_證照說明與問卷結果與課程說明

02_下載懶人包與解壓縮並執行

03_設定PYTHON資料路徑

04_新增專案與模組並撰寫程式

05_練習其他算術運算子與文字型態

06_修改編碼UTF8與轉型為文字

07_輸出變數資料型態與脫逸字元

08_下周預告與回家練習

完整教學

http://goo.gl/aQTMFS

吳老師教學論壇

http://www.tqc.idv.tw/

教學論壇(之後課程會放論壇上課學員請自行加入):

https://groups.google.com/forum/#!forum/tcfst_python_2020_2

TQC+基礎程式語言 (Python 3)證照

Python 第1類:基本程式設計

技能內容:變數與常數、指定敘述、標準輸入輸出、運算式、算術運算子、數學函式的應用、格式化的輸出Python 第2類:選擇敘述

技能內容:if、if...else、if…elifPython 第3類:迴圈敘述

技能內容:while、for…inPython 第4類:進階控制流程

技能內容:常用的控制結構、條件判斷、迴圈Python 第5類:函式(Function)

技能內容:函式使用、傳遞參數、回傳資料、內建函式、區域變數與全域變數

上課用書:

Python 3.x 程式語言特訓教材(第二版)

作者: 蔡明志, 財團法人中華民國電腦技能基金會

出版社:全華

出版日期:2018/12/20

定價:490元

吳老師 109/5/5

EXCEL,VBA,Python,自強工業基金會,EXCEL,VBA,函數,程式設計,線上教學,PYTHON安裝環境

以時序錯誤導向電軌調變技術實現之細緻化電壓調節及其於能耗可調數位系統之應用

為了解決資料路徑 的問題,作者陳威仁 這樣論述:

電壓調節技術(voltage scaling)在提高數位系統的能源效益方面具有相當大的潛力。然而,其節能效益在極大程度上受制於系統中穩壓電路之性能。本論文旨在提出一種可打破此限制的基於時序錯誤導向之電源軌調變技術,並以此技術實現細緻化的電壓調節。所提出之技術只需要少數電壓檔位,即可利用電源軌抖動(supply rail voltage dithering)的方式來近似出細緻化電壓調節的效果。因此,所提出之方法可以顯著降低晶片內穩壓電路的設計開銷。由於數位式低壓降線性穩壓器(digital low-dropout regulator, DLDO)具有無縫整合:(一)穩定輸出電壓、(二)電源軌抖

動、以及(三)電源閘控(power gating)等技術之特性,因此本論文利用DLDO來實現所提出之電源軌調變技術。為了精確與快速地實現適用於不同應用場景之DLDO電路,本論文也提出一種具有快速週轉時間的DLDO設計方法,並實際以一高性能DLDO設計為例驗證其效益。實驗結果指出,使用了聯電110奈米製程所製造的DLDO測試晶片展現出3毫伏特的超低漣波、67奈秒的輕載至重載暫態響應及250奈秒的重載至輕載暫態響應。與最先進的DLDO設計相比,該DLDO具有更簡潔的硬體架構且在品質因數(figure of merit)方面展現出高度競爭力。而後,本文以一種基於DLDO的抖動電源 (dithered

power supply)來實現所提出之電源軌調變技術。為了驗證所提出技術之效益,我們使用了一個具有時序錯誤偵測與修正能力之可程式化DSP資料路徑(datapath)作為測試載體。此測試晶片以台積電65奈米低功耗製程實現,而研究結果表明,所提出之電源軌調變技術有助於回收設計階段時留下之保守設計餘裕(design margin)並提高能源效率。量測結果指出,當該DSP資料路徑被程式化為一個無限脈衝響(infinite impulse response)數位濾波器以執行低通濾波時,所提技術之節能效益最高可達30.8%。最後,本論文將所提出之電源軌調變技術應用於即時影像處理系統中並探索其先天的容錯

能力。我們利用人眼視覺可將視訊中相鄰影格及影格中鄰近畫素進行視覺積分的特性,來達到即使不須對時序錯誤進行主動偵測及修正也能維持一定視覺品質的效果。因此,藉由巧妙安排容許時序錯誤發生之位置(藉由降低操作電壓),因時序錯誤所產生的錯誤畫素即可主動被人眼濾除。 該測試晶片以聯電40奈米製程實現,其搭載了一個即時視訊縮放引擎作為測試載具。在實驗結果中,該測試晶片展現了高達35%的節能效益,並能在不需對時序錯誤做出任何修正、且不須更動資料路徑架構的狀況下,仍能維持良好的主觀視覺感受。在五分制的平均主觀意見分數(mean opinion score)評量中,各類型的畫面皆達4分以上。而在客觀評量方面,峰值

信號雜訊比(peak signal-to-noise ratio)皆高於30分貝。

Xilinx Zynq-7000嵌入式系統設計與實現:基於Arm Cortex-A9雙核處理器和Vivado的設計方法(第二版)

為了解決資料路徑 的問題,作者何賓 這樣論述:

本書是作者在已經出版的《Xilinx Zynq-7000嵌入式系統設計與實現:基於ARM Cortex-A9雙核處理器和Vivado的設計方法》一書的基礎上進行修訂而成的。 本書新修訂後內容增加到30章。修訂後,本書的一大特色就是加入了Arm架構及分類、使用PetaLinux工具在Zynq-7000 SoC上搭建Ubuntu作業系統,以及在Ubuntu作業系統環境下搭建Python語言開發環境,並使用Python語言開發應用程式的內容。 本書修訂後。進一步降低了讀者學習Arm Cortex-A9嵌入式系統的門檻,並引入了在Zynq-7000 SoC上搭建Ubuntu作業系統的新方法。此

外,將流行的Python語言引入到Arm嵌入式系統中,進一步拓寬了在Arm嵌入式系統上開發應用程式的方法。 第1章 Zynq - 7000 SoC設計導論 1 1.1 全可程式設計片上系統基礎知識 1 1.1.1 全可程式設計片上系統的演進 1 1.1.2 SoC與MCU和CPU的比較 3 1.1.3 全可程式設計SoC誕生的背景 4 1.1.4 可程式設計SoC系統技術特點 5 1.1.5 全可程式設計片上系統中的處理器類型 5 1.2 Arm架構及分類 6 1.2.1 M - Profile 7 1.2.2 R - Profile 9 1.2.3 A - Profile

10 1.3 Zynq - 7000 SoC功能和結構 11 1.3.1 Zynq - 7000 SoC產品分類及資源 12 1.3.2 Zynq - 7000 SoC的功能 12 1.3.3 Zynq - 7000 SoC處理系統PS的構成 14 1.3.4 Zynq - 7000 SoC可程式設計邏輯PL的構成 19 1.3.5 Zynq - 7000 SoC內的互聯結構 20 1.3.6 Zynq - 7000 SoC的供電引腳 22 1.3.7 Zynq - 7000 SoC內MIO到EMIO的連接 23 1.3.8 Zynq - 7000 SoC內為PL分配的信號 28 1.4 Z

ynq - 7000 SoC在嵌入式系統中的優勢 30 1.4.1 使用PL實現軟體演算法 30 1.4.2 降低功耗 32 1.4.3 即時減負 33 1.4.4 可重配置計算 34 第2章 AMBA規範 35 2.1 AMBA規範及發展 35 2.1.1 AMBA 1 36 2.1.2 AMBA 2 36 2.1.3 AMBA 3 36 2.1.4 AMBA 4 37 2.1.5 AMBA 5 38 2.2 AMBA APB規範 40 2.2.1 AMBA APB寫傳輸 40 2.2.2 AMBA APB讀傳輸 42 2.2.3 AMBA APB錯誤回應 43 2.2.4 操作狀態 44

2.2.5 AMBA 3 APB信號 44 2.3 AMBA AHB規範 45 2.3.1 AMBA AHB結構 45 2.3.2 AMBA AHB操作 46 2.3.3 AMBA AHB傳輸類型 48 2.3.4 AMBA AHB猝發操作 50 2.3.5 AMBA AHB傳輸控制信號 53 2.3.6 AMBA AHB位址解碼 54 2.3.7 AMBA AHB從設備傳輸回應 55 2.3.8 AMBA AHB資料匯流排 58 2.3.9 AMBA AHB傳輸仲裁 59 2.3.10 AMBA AHB分割傳輸 64 2.3.11 AMBA AHB復位 67 2.3.12 關於AHB資料匯

流排的位元寬 67 2.3.13 AMBA AHB周邊設備 68 2.4 AMBA AXI4規範 69 2.4.1 AMBA AXI4概述 69 2.4.2 AMBA AXI4功能 70 2.4.3 AMBA AXI4互聯結構 78 2.4.4 AXI4 - Lite功能 79 2.4.5 AXI4 - Stream功能 80 第3章 Zynq - 7000系統公共資源及特性 83 3.1 時鐘子系統 83 3.1.1 時鐘子系統架構 83 3.1.2 CPU時鐘域 84 3.1.3 時鐘程式設計實例 86 3.1.4 時鐘子系統內的生成電路結構 87 3.2 復位子系統 91 3.2.1

重定子系統結構和層次 92 3.2.2 重定流程 93 3.2.3 復位的結果 94 第4章 Zynq調試和測試子系統 95 4.1 JTAG和DAP子系統 95 4.1.1 JTAG和DAP子系統功能 97 4.1.2 JTAG和DAP子系統I/O信號 99 4.1.3 程式設計模型 99 4.1.4 Arm DAP控制器 101 4.1.5 跟蹤埠介面單元(TPIU) 102 4.1.6 Xilinx TAP控制器 102 4.2 CoreSight系統結構及功能 103 4.2.1 CoreSight結構概述 103 4.2.2 CoreSight系統功能 104 第5章 Corte

x - A9處理器及指令集 107 5.1 應用處理單元概述 107 5.1.1 基本功能 107 5.1.2 系統級視圖 108 5.2 Cortex - A9處理器結構 110 5.2.1 處理器模式 111 5.2.2 寄存器 113 5.2.3 流水線 118 5.2.4 分支預測 118 5.2.5 指令和資料對齊 119 5.2.6 跟蹤和調試 121 5.3 Cortex - A9處理器指令集 122 5.3.1 指令集基礎 122 5.3.2 資料處理操作 125 5.3.3 記憶體指令 130 5.3.4 分支 131 5.3.5 飽和算術 133 5.3.6 雜項指令 13

4 第6章 Cortex - A9片上記憶體系統結構和功能 138 6.1 L1快取記憶體 138 6.1.1 快取記憶體背景 138 6.1.2 快取記憶體的優勢和問題 139 6.1.3 記憶體層次 140 6.1.4 快取記憶體結構 140 6.1.5 緩存策略 145 6.1.6 寫和取緩衝區 147 6.1.7 緩存性能和命中速度 147 6.1.8 無效和清除緩存 147 6.1.9 一致性點和統一性點 149 6.1.10 Zynq - 7000中Cortex - A9 L1快取記憶體的特性 151 6.2 記憶體順序 153 6.2.1 普通、設備和強順序記憶體模型 154

6.2.2 記憶體屬性 155 6.2.3 記憶體屏障 155 6.3 記憶體管理單元 159 6.3.1 MMU功能描述 160 6.3.2 虛擬記憶體 161 6.3.3 轉換表 162 6.3.4 頁表入口域的描述 165 6.3.5 TLB構成 167 6.3.6 記憶體訪問順序 169 6.4 偵聽控制單元 170 6.4.1 地址過濾 171 6.4.2 SCU主設備埠 171 6.5 L2快取記憶體 171 6.5.1 互斥L2 - L1快取記憶體配置 173 6.5.2 快取記憶體替換策略 174 6.5.3 快取記憶體鎖定 174 6.5.4 使能/禁止L2快取記憶體控制器

176 6.5.5 RAM訪問延遲控制 176 6.5.6 保存緩衝區操作 176 6.5.7 在Cortex - A9和L2控制器之間的優化 177 6.5.8 預取操作 178 6.5.9 程式設計模型 179 6.6 片上記憶體 180 6.6.1 片上記憶體概述 180 6.6.2 片上記憶體功能 181 6.7 系統位址分配 186 6.7.1 位址映射 186 6.7.2 系統匯流排主設備 188 6.7.3 I/O外設 188 6.7.4 SMC記憶體 188 6.7.5 SLCR寄存器 188 6.7.6 雜項PS寄存器 189 6.7.7 CPU私有寄存器 189 第7章

Zynq - 7000 SoC的Vivado基本設計流程 190 7.1 創建新的工程 190 7.2 使用IP集成器創建處理器系統 192 7.3 生成頂層HDL並匯出設計到SDK 197 7.4 創建應用測試程式 199 7.5 設計驗證 202 7.5.1 驗證前的硬體平臺準備 202 7.5.2 設計驗證的具體實現 203 7.6 SDK調試工具的使用 205 7.6.1 打開前面的設計工程 205 7.6.2 導入工程到SDK 205 7.6.3 建立新的記憶體測試工程 205 7.6.4 運行記憶體測試工程 206 7.6.5 調試記憶體測試工程 207 7.7 SDK性能分析工具

209 第8章 Arm GPIO的原理和控制實現 213 8.1 GPIO模組原理 213 8.1.1 GPIO介面及功能 214 8.1.2 GPIO程式設計流程 217 8.1.3 I/O介面 218 8.1.4 部分寄存器說明 218 8.1.5 底層讀/寫函數說明 220 8.1.6 GPIO的API函數說明 220 8.2 Vivado環境下MIO讀/寫控制的實現 221 8.2.1 調用底層讀/寫函數編寫GPIO應用程式 221 8.2.2 調用API函數編寫控制GPIO應用程式 224 8.3 Vivado環境下EMIO讀/寫控制的實現 226 8.3.1 調用底層讀/寫函數

編寫GPIO應用程式 227 8.3.2 調用API函數編寫控制GPIO應用程式 232 第9章 Cortex - A9異常與中斷原理及實現 236 9.1 異常原理 236 9.1.1 異常類型 237 9.1.2 異常處理 241 9.1.3 其他異常控制碼 242 9.1.4 Linux異常程式流 243 9.2 中斷原理 244 9.2.1 外部插斷要求 244 9.2.2 Zynq - 7000 SoC內的中斷環境 247 9.2.3 中斷控制器的功能 248 9.3 Vivado環境下中斷系統的實現 252 9.3.1 Cortex - A9處理器中斷及異常初始化流程 252 9

.3.2 Cortex - A9 GPIO控制器初始化流程 252 9.3.3 匯出硬體設計到SDK 253 9.3.4 創建新的應用工程 253 9.3.5 運行應用工程 256 第10章 Cortex - A9計時器原理及實現 257 10.1 計時器系統架構 257 10.1.1 CPU私有計時器和看門狗計時器 257 10.1.2 全域計時器/計數器 258 10.1.3 系統級看門狗計時器 259 10.1.4 3重計時器/計數器 261 10.1.5 I/O信號 264 10.2 Vivado環境下計時器的控制實現 264 10.2.1 打開前面的設計工程 265 10.2.2

創建SDK軟體工程 265 10.2.3 運行軟體應用工程 267 第11章 Cortex - A9 DMA控制器原理及實現 268 11.1 DMA控制器架構 268 11.2 DMA控制器功能 271 11.2.1 考慮AXI交易的因素 272 11.2.2 DMA管理器 273 11.2.3 多通道資料FIFO(MFIFO) 274 11.2.4 記憶體―記憶體交易 274 11.2.5 PL外設AXI交易 274 11.2.6 PL外設請求介面 275 11.2.7 PL外設長度管理 276 11.2.8 DMAC長度管理 277 11.2.9 事件和中斷 278 11.2.10 異

常終止 278 11.2.11 安全性 280 11.2.12 IP配置選項 282 11.3 DMA控制器程式設計指南 282 11.3.1 啟動控制器 282 11.3.2 執行DMA傳輸 282 11.3.3 插斷服務常式 282 11.3.4 寄存器描述 283 11.4 DMA引擎程式設計指南 284 11.4.1 寫微代碼程式設計用於AXI交易的CCRx 284 11.4.2 記憶體到記憶體傳輸 284 11.4.3 PL外設DMA傳輸長度管理 287 11.4.4 使用一個事件重新啟動DMA通道 289 11.4.5 中斷一個處理器 289 11.4.6 指令集參考 290 11

.5 程式設計限制 291 11.6 系統功能之控制器重定配置 292 11.7 I/O介面 293 11.7.1 AXI主介面 293 11.7.2 外設請求介面 293 11.8 Vivado環境下DMA傳輸的實現 294 11.8.1 DMA控制器初始化流程 295 11.8.2 中斷控制器初始化流程 295 11.8.3 中斷服務控制碼處理流程 296 11.8.4 匯出硬體設計到SDK 296 11.8.5 創建新的應用工程 297 11.8.6 運行軟體應用工程 303 第12章 Cortex - A9安全性擴展 305 12.1 TrustZone硬體架構 305 12.1.1

多核系統的安全性擴展 307 12.1.2 普通世界和安全世界的交互 307 12.2 Zynq - 7000 APU內的TrustZone 308 12.2.1 CPU安全過渡 309 12.2.2 CP15寄存器存取控制 310 12.2.3 MMU安全性 310 12.2.4 L1緩存安全性 311 12.2.5 安全異常控制 311 12.2.6 CPU調試TrustZone存取控制 311 12.2.7 SCU寄存器存取控制 312 12.2.8 L2緩存中的TrustZone支持 312 第13章 Cortex - A9 NEON原理及實現 313 13.1 SIMD 313

13.2 NEON架構 315 13.2.1 與VFP的共性 315 13.2.2 資料類型 316 13.2.3 NEON寄存器 316 13.2.4 NEON指令集 318 13.3 NEON C編譯器和彙編器 319 13.3.1 向量化 319 13.3.2 檢測NEON 319 13.4 NEON優化庫 320 13.5 SDK工具提供的優化選項 321 13.6 使用NEON內聯函數 324 13.6.1 NEON資料類型 325 13.6.2 NEON內聯函數 325 13.7 優化NEON彙編器代碼 327 13.8 提高記憶體訪問效率 328 13.9 自動向量化實現 329

13.9.1 匯出硬體設計到SDK 329 13.9.2 創建新的應用工程 330 13.9.3 運行軟體應用工程 331 13.10 NEON彙編代碼實現 331 13.10.1 匯出硬體設計到SDK 331 13.10.2 創建新的應用工程 332 13.10.3 運行軟體應用工程 333 第14章 Cortex - A9外設模組結構及功能 334 14.1 DDR記憶體控制器 334 14.1.1 DDR記憶體控制器介面及功能 335 14.1.2 AXI記憶體介面 337 14.1.3 DDR核和交易調度器 338 14.1.4 DDRC仲裁 338 14.1.5 DDR記憶體控制

器PHY 340 14.1.6 DDR初始化和標定 340 14.1.7 改錯碼 341 14.2 靜態記憶體控制器 342 14.2.1 靜態記憶體控制器介面及功能 343 14.2.2 靜態記憶體控制器和記憶體的信號連接 344 14.3 四 - SPI Flash控制器 345 14.3.1 四 - SPI Flash控制器功能 347 14.3.2 四 - SPI Flash控制器回饋時鐘 349 14.3.3 四 - SPI Flash控制器介面 349 14.4 SD/SDIO外設控制器 351 14.4.1 SD/SDIO控制器功能 352 14.4.2 SD/SDIO控制器傳輸

協議 353 14.4.3 SD/SDIO控制器埠信號連接 356 14.5 USB主機、設備和OTG控制器 356 14.5.1 USB控制器介面及功能 358 14.5.2 USB主機操作模式 361 14.5.3 USB設備操作模式 363 14.5.4 USB OTG操作模式 365 14.6 吉比特乙太網控制器 365 14.6.1 吉比特乙太網控制器介面及功能 367 14.6.2 吉比特乙太網控制器介面程式設計嚮導 368 14.6.3 吉比特乙太網控制器介面信號連接 372 14.7 SPI控制器 373 14.7.1 SPI控制器的介面及功能 374 14.7.2 SPI控制

器時鐘設置規則 376 14.8 CAN控制器 376 14.8.1 CAN控制器介面及功能 377 14.8.2 CAN控制器操作模式 379 14.8.3 CAN控制器消息保存 380 14.8.4 CAN控制器接收篩檢程式 381 14.8.5 CAN控制器程式設計模型 382 14.9 UART控制器 383 14.10 I2C控制器 387 14.10.1 I2C速度控制邏輯 388 14.10.2 I2C控制器的功能和工作模式 388 14.11 XADC轉換器介面 390 14.11.1 XADC轉換器介面及功能 391 14.11.2 XADC命令格式 392 14.11.3

供電感測器報警 392 14.12 PCI - E介面 393 第15章 Zynq - 7000內的可程式設計邏輯資源 395 15.1 可程式設計邏輯資源概述 395 15.2 可程式設計邏輯資源功能 396 15.2.1 CLB、Slice和LUT 396 15.2.2 時鐘管理 396 15.2.3 塊RAM 398 15.2.4 數位信號處理 - DSP Slice 398 15.2.5 輸入/輸出 399 15.2.6 低功耗串列收發器 400 15.2.7 PCI - E模組 401 15.2.8 XADC(類比 - 數位轉換器) 402 15.2.9 配置 402 第16章

Zynq - 7000內的互聯結構 404 16.1 系統互聯架構 404 16.1.1 互聯模組及功能 404 16.1.2 資料路徑 406 16.1.3 時鐘域 407 16.1.4 連線性 408 16.1.5 AXI ID 409 16.1.6 寄存器概述 409 16.2 服務品質 410 16.2.1 基本仲裁 410 16.2.2 不錯QoS 410 16.2.3 DDR埠仲裁 411 16.3 AXI_HP介面 411 16.3.1 AXI_HP介面結構及特點 411 16.3.2 介面資料寬度 415 16.3.3 交易類型 416 16.3.4 命令交替和重新排序 416

16.3.5 性能優化總結 416 16.4 AXI_ACP介面 417 16.5 AXI_GP介面 418 16.6 AXI信號總結 418 16.7 PL介面選擇 422 16.7.1 使用通用主設備埠的Cortex - A9 423 16.7.2 通過通用主設備的PS DMA控制器(DMAC) 423 16.7.3 通過高性能介面的PL DMA 426 16.7.4 通過AXI ACP的PL DMA 426 16.7.5 通過通用AXI從(GP)的PL DMA 426 第17章 Zynq - 7000 SoC內定制簡單AXI - Lite IP 429 17.1 設計原理 429 1

7.2 定制AXI - Lite IP 429 17.2.1 創建定制IP範本 429 17.2.2 修改定制IP設計範本 432 17.2.3 使用IP封裝器封裝外設 436 17.3 打開並添加IP到設計中 440 17.3.1 打開工程和修改設置 440 17.3.2 添加定制IP到設計 442 17.3.3 添加XDC約束檔 445 17.4 匯出硬體到SDK 446 17.5 建立和驗證軟體應用工程 446 17.5.1 建立應用工程 447 17.5.2 下載硬體位元流檔到FPGA 449 17.5.3 運行應用工程 450 第18章 Zynq - 7000 SoC內定制複雜AX

I Lite IP 451 18.1 設計原理 451 18.1.1 VGA IP核的設計原理 451 18.1.2 移位暫存器IP核的設計原理 453 18.2 定制VGA IP核 454 18.2.1 創建定制VGA IP範本 454 18.2.2 修改定制VGA IP範本 455 18.2.3 使用IP封裝器封裝VGA IP 459 18.3 定制移位暫存器IP核 460 18.3.1 創建定制SHIFTER IP範本 460 18.3.2 修改定制SHIFTER IP範本 462 18.3.3 使用IP封裝器封裝SHIFTER IP 463 18.4 打開並添加IP到設計中 464 1

8.4.1 打開工程和修改設置 464 18.4.2 添加定制IP到設計 466 18.4.3 添加XDC約束檔 470 18.5 匯出硬體到SDK 471 18.6 建立和驗證軟體工程 472 18.6.1 建立應用工程 472 18.6.2 下載硬體位元流檔到FPGA 476 18.6.3 運行應用工程 477 第19章 Zynq - 7000 AXI HP資料傳輸原理及實現 478 19.1 設計原理 478 19.2 構建硬體系統 479 19.2.1 打開工程和修改設置 479 19.2.2 添加並連接AXI DMA IP核 480 19.2.3 添加並連接FIFO IP核 482

19.2.4 連接DMA中斷到PS 485 19.2.5 驗證和建立設計 487 19.3 建立和驗證軟體工程 487 19.3.1 匯出硬體到SDK 488 19.3.2 創建軟體應用工程 488 19.3.3 下載硬體位元流檔到FPGA 497 19.3.4 運行應用工程 497 第20章 Zynq - 7000 ACP資料傳輸原理及實現 499 20.1 設計原理 499 20.2 打開前面的設計工程 499 20.3 配置PS埠 499 20.4 添加並連接IP到設計 500 20.4.1 添加IP到設計 501 20.4.2 系統連接 501 20.4.3 分配位址空間 502

20.5 使用SDK設計和實現應用工程 504 20.5.1 創建新的軟體應用工程 504 20.5.2 導入應用程式 504 20.5.3 下載硬體位元流檔到FPGA 507 20.5.4 運行應用工程 508 第21章 Zynq - 7000軟體和硬體協同調試原理及實現 509 21.1 設計目標 509 21.2 ILA核原理 510 21.2.1 ILA觸發器輸入邏輯 510 21.2.2 多觸發器埠的使用 510 21.2.3 使用觸發器和存儲限制條件 510 21.2.4 ILA觸發器輸出邏輯 512 21.2.5 ILA資料捕獲邏輯 512 21.2.6 ILA控制與狀態邏輯

513 21.3 VIO核原理 513 21.4 構建協同調試硬體系統 514 21.4.1 打開前面的設計工程 514 21.4.2 添加定制IP 514 21.4.3 添加ILA和VIO核 515 21.4.4 標記和分配調試網路 516 21.5 生成軟體工程 518 21.6 S/H協同調試 520 第22章 Zynq - 7000 SoC啟動和配置原理及實現 527 22.1 Zynq - 7000 SoC啟動過程 527 22.2 Zynq - 7000 SoC啟動要求 527 22.2.1 供電要求 528 22.2.2 時鐘要求 528 22.2.3 復位要求 528 22.

2.4 模式引腳 528 22.3 Zynq - 7000 SoC內的BootROM 530 22.3.1 BootROM特性 530 22.3.2 BootROM頭部 531 22.3.3 啟動設備 535 22.3.4 BootROM多啟動和開機磁碟分割查找 538 22.3.5 調試狀態 539 22.3.6 BootROM後狀態 540 22.4 Zynq - 7000 SoC器件配置介面 543 22.4.1 描述功能 544 22.4.2 器件配置流程 545 22.4.3 配置PL 549 22.4.4 寄存器概述 550 22.5 生成SD卡鏡像檔並啟動 551 22.5.1

SD卡與XC7Z020介面設計 551 22.5.2 打開前面的設計工程 552 22.5.3 創建級啟動引導 553 22.5.4 創建SD卡啟動鏡像 553 22.5.5 從SD卡啟動引導系統 555 22.6 生成QSPI Flash鏡像並啟動 556 22.6.1 QSPI Flash介面 556 22.6.2 創建QSPI Flash鏡像 557 22.6.3 從QSPI Flash啟動引導系統 558 22.7 Cortex - A9雙核系統的配置和運行 558 22.7.1 構建雙核硬體系統工程 558 22.7.2 添加並互聯IP核 559 22.7.3 匯出硬體設計到SDK中

561 22.7.4 設置板級包支援路徑 561 22.7.5 建立FSBL應用工程 562 22.7.6 建立CPU0應用工程 562 22.7.7 建立CPU1板級支持包 566 22.7.8 建立CPU1應用工程 566 22.7.9 創建SD卡鏡像文件 570 22.7.10 雙核系統運行和測試 571 22.7.11 雙核系統的調試 571 第23章 Zynq - 7000 SoC內XADC原理及實現 574 23.1 ADC轉換器介面結構 574 23.2 ADC轉換器功能 575 23.2.1 XADC的命令格式 576 23.2.3 供電感測器報警 576 23.3 XAD

C IP核結構及信號 577 23.4 開發平臺上的XADC介面 578 23.5 在Zynq - 7000 SoC內構建數模混合系統 579 23.5.1 打開前面的設計工程 579 23.5.2 配置PS埠 579 23.5.3 添加並連接XADC IP到設計 580 23.5.4 查看位址空間 582 23.5.5 添加用戶約束檔 583 23.5.6 設計處理 583 23.6 使用SDK設計和實現應用工程 584 23.6.1 生成新的應用工程 584 23.6.2 導入應用程式 585 23.6.3 下載硬體位元流檔到FPGA 591 23.6.4 運行應用工程 591 第24章

Linux開發環境的構建 592 24.1 構建虛擬機器環境 592 24.2 安裝和啟動Ubuntu 14.04客戶機作業系統 595 24.2.1 新添加兩個磁片 595 24.2.2 設置CD/DVD(SATA) 596 24.2.3 安裝Ubuntu 14.04 597 24.2.4 更改Ubuntu 14.04作業系統啟動設備 600 24.2.5 啟動Ubuntu 14.04作業系統 600 24.2.6 添加搜索連結資源 600 24.3 安裝FTP工具 601 24.3.1 Windows作業系統下LeapFTP安裝 601 24.3.2 Ubuntu作業系統環境下FTP安裝

602 24.4 安裝和啟動SSH和GIT組件 603 24.4.1 安裝和啟動SSH組件 603 24.4.2 安裝和啟動GIT組件 604 24.5 安裝交叉編譯器環境 604 24.5.1 安裝32位支援工具包 604 24.5.2 安裝和設置SDK 2015.4工具 605 24.6 安裝和配置Qt集成開發工具 606 24.6.1 Qt集成開發工具功能 606 24.6.2 構建PC平臺Qt環境 607 24.6.3 構建Arm平臺Qt環境 613 第25章 構建Zynq - 7000 SoC內Ubuntu硬體運行環境 622 25.1 建立新的設計工程 622 25.2 添加I

P核路徑 623 25.3 構建硬體系統 623 25.3.1 添加和配置ZYNQ7 IP 624 25.3.2 添加和配置VDMA IP核 625 25.3.3 添加和配置AXI Display Controller IP核 626 25.3.4 添加和配置HDMI Transmitter IP核 627 25.3.5 添加和配置VGA IP核 627 25.3.6 連接用戶自訂IP核 627 25.3.7 添加和配置Processor System Reset IP核 630 25.3.8 連接系統剩餘部分 630 25.4 添加設計約束檔 632 25.5 匯出硬體檔 633 第26章

構建Zynq - 7000 SoC內Ubuntu軟體運行環境 635 26.1 u - boot原理及實現 635 26.1.1 下載u - boot源碼 635 26.1.2 u - boot檔結構 636 26.1.3 u - boot工作模式 637 26.1.4 u - boot啟動過程 637 26.1.5 編譯u - boot 650 26.1.6 連結指令檔結構 652 26.2 內核結構及編譯 654 26.2.1 內核結構 654 26.2.2 下載Linux內核源碼 655 26.2.3 內核版本 655 26.2.4 內核系統組態 655 26.2.5 Bootload

er 啟動過程 658 26.2.6 Linux內核啟動過程 660 26.2.7 編譯內核 662 26.3 設備樹原理及實現 662 26.3.1 設備樹概述 662 26.3.2 設備樹資料格式 663 26.3.3 設備樹的編譯 664 26.4 檔案系統原理及下載 664 26.5 生成Ubuntu啟動鏡像 665 26.5.1 生成FSBL檔 666 26.5.2 生成BOOT.bin開機檔案 666 26.5.3 製作SD卡 668 26.5.4 複製BOOT. bin文件 670 26.5.5 複製編譯後的內核檔 670 26.5.6 複製編譯後的設備樹檔 671 26.5.7

複製檔案系統 671 26.6 啟動Ubuntu作業系統 672 第27章 Linux環境下簡單字元設備驅動程式的開發 674 27.1 驅動程式的必要性 674 27.2 Linux作業系統下的設備檔案類型 675 27.3 Linux驅動的開發流程 676 27.4 驅動程式的結構框架 676 27.4.1 載入和卸載函數模組 676 27.4.2 字元設備中重要的資料結構和函數 677 27.5 編寫makefile檔 683 27.6 編譯驅動程式 684 27.7 編寫測試程式 685 27.8 運行測試程式 686 第28章 Linux環境下包含中斷機制驅動程式的開發 688

28.1 設計原理 688 28.2 編寫包含中斷處理的驅動代碼 688 28.2.1 驅動程式標頭檔 688 28.2.2 驅動的載入和卸載函數 689 28.2.3 file_operations初始化 691 28.3 編寫makefile檔 691 28.4 編譯驅動程式 692 28.5 測試驅動程式 693 第29章 Linux環境下影像處理系統的構建 694 29.1 系統整體架構和功能 694 29.2 OV5640攝像頭性能 695 29.2.1 攝像頭捕獲模組的硬體 696 29.2.2 SCCB介面規範 696 29.2.3 寫攝像頭模組寄存器操作 697 29.2.

4 讀攝像頭模組寄存器操作 698 29.2.5 攝像頭初始化流程 700 29.3 Vivado HLS實現拉普拉斯運算元濾波演算法的設計 701 29.3.1 Vivado HLS工具的性能和優勢 701 29.3.2 拉普拉斯演算法與HDL之間的映射 703 29.4 影像處理系統的整體構建 706 29.5 影像處理系統軟體的設計 708 29.5.1 Ubuntu桌面系統的構建 708 29.5.2 Qt影像處理程式的開發 708 29.6 內嵌影像處理系統測試 710 第30章 Zynq-7000 SoC上構建和實現Python應用 712 30.1 設計所需的硬體環境 712

30.2 構建PetaLinux開發環境 712 30.2.1 PetaLinx開發環境概述 712 30.2.2 安裝32位庫 714 30.2.3 安裝並測試tftp伺服器 714 30.2.4 下載並安裝PetaLinux 715 30.3 構建嵌入式系統硬體 717 30.3.1 下載並安裝Vivado 2018.2整合式開發環境 717 30.3.2 添加板級支援包檔 717 30.3.3 建立新的Vivado工程 717 30.3.4 構建硬體系統 718 30.4 構建嵌入式Python開發環境 721 30.5 構建PC端Python開發環境 723 30.6 伺服器和用戶端P

ython的開發 724 30.6.1 伺服器端Python的開發 725 30.6.2 用戶端Python的開發 726 30.7 設計驗證 728 30.7.1 啟動伺服器程式 728 30.7.2 啟動用戶端程式 729

深度神經網路硬體加速器之資料路徑生成器設計與實作

為了解決資料路徑 的問題,作者鍾明學 這樣論述:

近年來,隨著科技的發展及硬體設備的進步,人工智慧(artificial intelligence, AI)的技術逐漸再次受到重視,舉凡影像辨識、目標分類等各方面都發展出各式各樣的深度神經網路模型。然而為了要追求更高的預測準確度,神經網路模型的層數也隨之增加並且使得計算更複雜,也因此在建構相對應的神經網路硬體加速器十,常常需要專屬的規格並花費大量的時間來設計與實作。此外有些硬體加速器也受限於頻寬或是硬體成本與設計,無法有效執行及加速某些深度神經網路模型的運算。本論文首先分析目前較常使用的深度神經網路模型,然後設計可以執行這些模型運算的硬體加速器資料路徑,包含CNN運算、激活層、池化層等,再用這

些深度神經網路模型測試此硬體加速器資料路徑的效能。本論文除了設計通用的深度神經網路硬體加速器資料路徑,也另外設計特定的深度神經網路資料路徑生成器,讓使用者可以針對不同的神經網路模型,自動產生相對應的硬體加速資料路徑,而不需要花費時間與人力來修改通用的深度神經網路硬體加速器,並且達到比較好的加速效果。

資料路徑的網路口碑排行榜

-

#1.[我的文件] 資料夾的設定- Microsoft 支援服務

如何變更[我的文件] 資料夾儲存位置 · 以滑鼠右鍵按一下[ 我的文件] (在桌面),然後按一下[ 屬性]。 · 在[ 目標] 方塊中,輸入[我的文件] 資料夾的新路徑,或按一下[ 移動] ... 於 support.microsoft.com -

#2.在命令提示字元取得目前資料夾路徑的方法 - 簡睿隨筆

Windows學習誌 / 生產力工具 · 0. 在命令提示字元取得目前資料夾路徑的方法—使用set /p|初學者的命令行#10. 由 簡睿 · 發表於: 2021/04/22 · 更新於: 2021/04/22. 於 jdev.tw -

#3.Microsoft Store 版本App 的資料儲存 - Heresy's Space

安裝路徑. Program Files. Windows 最典型的應用程式安裝路徑,以現在都是x64 的電腦來說,基本上就是:. 於 kheresy.wordpress.com -

#4.颱風消息| 交通部中央氣象局

路徑 潛勢預測圖的目的在表示颱風中心未來可能移入的範圍。 ... 本產品為機率預報圖之一種,係將最新的颱風預測資料以及過去預測誤差的統計特性綜合而成。 於 www.cwb.gov.tw -

#5.不間斷Python 挑戰Day 27 - 檔案、資料夾與路徑|方格子vocus

file:檔案路徑; mode:打開文件的模式,預設為'r',意即僅供讀取。可用的模式有: ... 今天將介紹檔案的讀寫、資料夾與路徑。 持續學習! 於 vocus.cc -

#6.Windows 系統中資料路徑太長無法刪除的解決辦法 - demo小鋪

Windows 的檔案路徑最長只能有260 個字元,在都是Windows 環境中不容易遇到這問題,但在開始往Open Source 靠攏後這就變成一個無法避免的問題了,本篇 ... 於 demo.tc -

#7.HTML 網址與路徑 - STEAM 教育學習網

等,此外,這些路徑又分成絕對路徑和相對路徑,這篇教學會介紹HTML 網址路徑的觀念與用法。 ... 路徑:檔案開啟的路徑,例如在資料夾X 中開啟的A.html,其路徑可能 ... 於 steam.oxxostudio.tw -

#8.【清理硬碟】C槽空間不足嗎?教你如何清出更多的空間來

從C槽中清除不需要的資料 佔據我們C磁碟空間的資料約可歸納以下幾類: – 所安裝的應用 ... 實際路徑為「C:\Users\(您的使用者名稱)\AppData\Local\Temp」,如下圖:. 於 www.htjh.ntpc.edu.tw -

#9.適用於動態頂層目錄路徑的Linux 和Unix 檔案系統排除選項 - Dell

Avamar Linux 或Unix 檔案系統附掛程式通常會在Avamar 資料集排除清單中使用絕對路徑,如有需要,則可使用萬用字元來符合其他必要的條件。 如果需要排除的資料位置發生 ... 於 www.dell.com -

#10.在64位元資料路徑上實行128位元simd操作

這允許通過軟體與硬體處理器交互的使用者提供資料路徑位元寬而不是寄存器位元寬的資料。優勢在於,用戶可以不知道寄存器的大小。 於 patents.google.com -

#11.移動Steam 及遊戲安裝位置

要將現有的遊戲安裝資料夾移至同一台電腦上不同的位置,可以使用Steam 的「移動」功能。 請完成以下步驟來使用此選項:. 確保您建立了可將檔案移入的不同Steam 收藏庫路徑 ... 於 help.steampowered.com -

#12.檢視資料存放區路徑 - VMware Docs

檢閱連線到支援VMFS 資料存放區的儲存裝置的路徑。 程序. 在vSphere Client 中,導覽至資料存放區。 按一下 ... 於 docs.vmware.com -

#13.如何變更SQL Server 預設的資料檔路徑與備份檔路徑

當你安裝好SQL Server 2005/2008 之後,通常相關檔案的預設安裝路徑都會在C:\Program Files\Microsoft SQL Server\MSSQL.2\MSSQL 目錄下,而該目錄下 ... 於 blog.miniasp.com -

#14.Q.影印機掃描成功,但找不到資料存在哪?路徑檢查(FTP)

金儀提供影印機掃描後存檔路徑檢查教學步驟:1.開啟FTP程式2.點選Browse 3.確認存檔資料夾路徑,影印機掃描、影印機設定請洽4128-566. 於 www.oa-world.com.tw -

#15.Chapter 1 掌握你的電腦| RLads Lab

1.1 路徑& 工作目錄. 電腦透過資料夾(directory) 與檔案(file) 將資訊組織起來,方便與使用者互動。資料夾裡面可以是另一個資料夾,也可以是檔案。換言之,資料夾是有 ... 於 rlads2021.github.io -

#16.MacMoney 麥克錢包- 使用說明- 資料路徑設至Dropbox

這個功能就是把MacMoney 的資料儲存路徑改到Dropbox 目錄內,透過Dropbox 的同步功能讓多台Mac 能夠存取相同的資料。 設定方式: 使用時先進入MacMoney 的偏好設定作設定. 於 www.devon.riceball.net -

#17.簡易terminal教學 - GitHub Gist

簡易terminal指令. 指令總覽. ls 顯示當前目錄下的檔案; mkdir 資料夾的名稱 建立一個新的資料夾; cd 路徑 移動到指定的路徑; rm 檔案 移除檔案; mv 原檔案/路徑新 ... 於 gist.github.com -

#18.如何快速列出資料夾內所有檔案路徑 - lazyorangelife

想列出資料夾內的檔案路徑,難道只能點選右鍵-「內容」-「安全性」-「物件名稱」,將檔案路徑逐一紀錄? 不用這麼麻煩,以下簡單帶你快速列出資料夾內所有檔案路徑。 於 lazyorangelife.com -

#19.e化服務系統: 投保單位網路申報及查詢作業 - 勞動部勞工保險局

路徑 :投保單位網路申報及查詢作業/資料查詢/勞工退休金計算名冊下載,點選【逕調名冊下載】按鈕。 112年5月份保險費及勞工退休金繳款單背面印製通函提醒投保(提繳)單位 ... 於 edesk.bli.gov.tw -

#20.【網路教學】相對路徑與絕對路徑 - 網頁設計

絕對路徑指的是這個檔案在本機端或是網路上的絕對位置。以範例來說像「D: 近期使用檔案」這句所描述的就是「在這台電腦D 槽裡面近期使用檔案這個資料夾」, ... 於 www.injerry.com -

#21.如何快速列出資料夾內所有檔案路徑 - YouTube

想列出 資料 夾內的檔案 路徑 ,難道只能將檔案 路徑 逐一紀錄?不用這麼麻煩,以下簡單帶你快速列出 資料 夾內所有檔案 路徑 。更詳細的 資料 可點選 ... 於 www.youtube.com -

#22.在Mac 上取得檔案、檔案夾和磁碟資訊 - Apple Support

每個項目會開啟一個資訊視窗。 顯示檔案或檔案夾的路徑. 在Mac 上,按一下Dock 中的Finder 圖像 來 ... 於 support.apple.com -

#23.路徑遍歷

檢查指定檔案是否為預期的目標,以免資料外洩或權限變更出錯。 檢查目前的作業目錄是否與標準路徑的傳回值完全相同。 確保權限系統明確限定在作業範圍內, ... 於 developer.android.com -

#24.Python — 使用檔案系統. 包含檔案的路徑 - Medium

使用os.path.basename(),會擷取路徑最後的資料夾或檔案名稱。 os.path.basename(filr_url). 承上,這個程式碼會取得的結果是csv。因為csv是最後 ... 於 medium.com -

#25.檔案總管要怎麼顯示完整路徑? - iT 邦幫忙

開啟檔案總管-->工具-->資料夾選項-->檢視-->勾選在網址列顯示完整路徑在標題列顯示完整路徑搜尋檔案完成後-->檢視-->詳細資料以上是XP系統 於 ithelp.ithome.com.tw -

#26.欲設定人體模型資料庫路徑 - PTC Support

按一下「組態編輯器」(Configuration Editor)。「檢視和管理Creo Parametric 選項」(View and manage Creo Parametric options) 頁會開啟,且其中包含最新載入或匯入的 ... 於 support.ptc.com -

#27.系統選項-檔案路徑

應用程式路徑, V, V, 40, 工作站的系統主路徑,本目錄的預設名稱為Wcir. 系統程式路徑, V ... 系統程式路徑, V, 40, 存放VFP版本資料庫檔案位置. 主要資料庫路徑 ... 於 www.mcleo.idv.tw -

#28.[教學] Windows 10 我的文件系統檔案位置路徑變更移動至D 槽 ...

隨著電腦長時間使用,會發現到系統槽當中個人檔案越來越肥大,尤其是當初買小容量SSD 固態硬碟空間很吃緊,那麼就得要把這些資料移到其他資料存放硬碟中。 檢查了一下也 ... 於 sofun.tw -

#29.[Mac] 在Finder 中快速複製路徑、開啟指定資料夾

[Mac] 在Finder 中快速複製路徑、開啟指定資料夾 ... 以前在Windows 的檔案總管,很習慣複製某個目錄的完整路徑後,. 直接貼在位址列上,就可以跳到 ... 於 ephrain.net -

#30.Windows 10/11的Documents 文件夾在哪裡? - 挨踢路人甲

預設狀態下,安裝Windows 11/10 時,documents文件夾會在你的帳戶下建立,也就是路徑為C:\Users\帳戶名稱\Documents,快速存取下的文件資料夾只是個 ... 於 walker-a.com -

#31.如何知道python直接讀取的資料夾路徑? - Cupoy

如何知道python直接讀取的資料夾路徑? ... 當你只寫「部分位置或是檔名」的話,稱為是「相對路徑」,相對位置是以程式所在的位置做為預設的位置。舉個例子,如果你只有寫data ... 於 www.cupoy.com -

#32.複製檔案路徑 - Fujifilm

說明將檔案或資料夾的完整路徑複製到剪貼簿的方法。 程式. 1. 在工作區選擇檔案。 資料夾時,則在資料夾區或工作區選擇。 2. 選擇[檔案] 選單的[複製路徑]。 於 opencds-fb.fujifilm.com -

#33.在檔案總管中複製路徑與檔名@ 寶來的紅色天葵子 - 隨意窩

這樣的操作可以適用於檔案總管中的資料夾,也適用於桌面上的檔案。您可以自己在桌面上,練習看看。 <. p>. 引用:http://7club.ithome.com.tw ... 於 m.xuite.net -

#34.目錄與路徑

目錄與路徑 · cd (Change Directory):變換工作目錄。 · pwd (Print Working Directory):顯示目前所在的目錄。 · mkdir (Make Directory):建立新目錄。 · rmdir (Remove ... 於 dywang.csie.cyut.edu.tw -

#35.如何從Mac上的Finder複製檔案或資料夾路徑?

無法從Mac中的Finder直接複製檔案或資料夾路徑。有三種方法可以做到這一點,我們在這裡都提到過。 於 www.maccleanerfree.com -

#36.HP LaserJet Pro MFP - 設定「掃描至網路資料夾」功能

開始設定程序之前,管理員需要下列資訊。 對印表機的管理存取權限. 目的地資料夾的網路路徑(例如\\servername. 於 support.hp.com -

#37.在Tableau 中建立顯示起點和終點之間的路徑的地圖

請按照此主題中的範例瞭解如何設定資料來源並為兩個不同的蜘蛛圖組建檢視。 有關可能更適合您的資料的其他範例,請參閱Tableau Public 上的以下工作簿:. Puget Sound ... 於 help.tableau.com -

#38.烏克蘭入盟白宮:北約將提出改革路徑- 新聞- Rti 中央廣播電臺

烏克蘭入盟白宮:北約將提出改革路徑 白宮國家安全顧問蘇利文(Jake Sullivan)。(資料照/AFP). 白宮國家安全顧問蘇利文(Jake Sullivan)今天(11日) ... 於 www.rti.org.tw -

#39.劃分轉換路徑資料- Analytics (分析)說明 - Google Support

劃分轉換路徑資料. 「轉換區隔」可讓您隔離並分析「多管道程序報表」中的某組轉換路徑。舉例來說,您可以建立一個轉換區隔,其中的程序只包含最初互動為某個金額以上的 ... 於 support.google.com -

#40.資料路徑與控制路徑介面

開始安裝前,您必須先建立下列Enterprise Tape Library 3494 通訊:. CA ARCserve Backup 伺服器與Enterprise Tape Library 3494 磁帶機之間的SCSI 或光纖通道資料路徑。 於 ftpdocs.broadcom.com -

#41.資料路徑端到端保護 - ADATA INDUSTRIAL

當資料被讀取或寫入時,其行走路徑會經過不同的站點。寫入的路徑包含Host -->PCIe IP-->Data Buffer-->Flash IP-->NAND Flash,讀取的路徑則是反 ... 於 industrial.adata.com -

#42.C語言下確認一個檔案的絕對路徑 - 力場產生器的黑盒子

在stackoverflow逛到的答案是,使用 realpath 或 readlink 。當然,我們也可以利用「當前資料夾+檔案相對路徑」的方法來建立出絕對路徑,但有個函數來幫 ... 於 starforcefield.wordpress.com -

#43.路徑(Solaris 一般桌上管理系統環境:使用者指南)

(請參閱如果要配置標頭 以取得更多資料。) 路徑和路徑名稱. 物件的路徑是設定物件在檔案系統內位置的方法。有兩個方法可以設定路徑:絕對 ... 於 docs.oracle.com -

#44.在與運行VI同資料夾中增加檔案路徑- NI

您可以使用 Application Directory.vi 並直接建構所需檔案的路徑位置,如以下程式碼片段所示:. 另外,您可以在LabVIEW中使用 Current VI's Path 回傳呼叫 ... 於 knowledge.ni.com -

#45.無法在資料夾位址路徑中使用LDAP 屬性| Lexmark CX820

無法在資料夾位址路徑中使用LDAP 屬性. 請嘗試下列其中一個或多個項目:. 請務必在屬性前後輸入%. 聯絡管理員. 您的管理員可以讓您建立資料夾,並可正確配置LDAP 設定 ... 於 infoserve.lexmark.com -

#46.Path Copy Copy 20.0.0 – 一鍵複製檔案完整路徑 - 中文化天地網-

安裝後會在右鍵選單新增兩個功能表,分別是「Copy File/Folder Path」的一級功能表和「Path Copy」的二級功能表,前者直接就可以複製檔案/資料夾完整的路徑位址,後者 ... 於 zhtwnet.com -

#47.[ Windows ] 如何利用快速鍵快速複製檔案完整路徑? - 關鍵應用

當要取得Windows 資料夾或檔案完整路徑時,很多人可能會想到利用滑鼠右鍵點擊後,再去複製[ 內容]內的位置屬型,但這樣的操作,只會取出路徑,卻沒有檔案或資料夾的 ... 於 key.chtouch.com -

#48.掛載遠端資料夾| File Station - Synology 知識中心

按一下工具> 掛載遠端資料夾> CIFS 共用資料夾。 · 在資料夾欄位中,以 \\網域名稱\遠端資料夾 或 \\遠端伺服器IP\遠端資料夾 格式指定遠端資料夾路徑,例如: \\chad\ ... 於 kb.synology.com -

#49.【C# Form】瀏覽資料夾路徑 - 菲特茶的程式筆記- FC2

最近在寫一些專案用的工具,用的是C#的Form 然後有一個"瀏覽資料夾"路徑的功能,意外的網路討論數沒有很多 簡單來說就是點了瀏覽的按紐,然後出現像 ... 於 teafatesanya.blog.fc2.com -

#50.如何修改TP辦公通資料儲存的路徑?

按一下左上角個人圖像> 「本機資料」>「修改路徑」。 以「接收的檔案」為例: 1. 按一下「接收的檔案」右側的「修改路徑」按鈕。如果您要還原為預設設定, ... 於 www.teampel.com -

#51.Python pathlib 教學:檔案路徑操作超簡單,不再煩惱前斜線或 ...

不論哪個作業系統,在Path 物件內部,一律用前斜線(/)儲存路徑資料; 然而,當你用print() 或是str() 來表示Path 的路徑字串,Path 物件會幫你依據 ... 於 haosquare.com -

#52.第六章、Linux 檔案與目錄管理 - 鳥哥私房菜

因為/var/mail 是連結檔,連結到/var/spool/mail # 所以,加上pwd -P 的選項後,會不以連結檔的資料顯示,而是顯示正確的完整路徑啊! pwd是Print Working Directory的 ... 於 linux.vbird.org -

#53.路徑排除格式

代表一個字元,而星號(*) 代表含有零或多個字元的字串。 example. 排除格式. •如果您想要排除資料夾中 ... 於 help.eset.com -

#54.遠端路徑名稱必須是資料目錄的相對路徑

發生情況在Windows ™ 中,您已選擇「 檔案> 應用程式> 新增」或「 檔案> 抄寫> 新抄本」,以在HCL Domino ® 伺服器上建立應用程式,但您卻嘗試在伺服器的資料目錄外部 ... 於 help.hcltechsw.com -

#55.資料路徑之自動合成__臺灣博碩士論文知識加值系統

資料路徑 的組成是矽編輯器裡相當重要的一環,在過去幾年中,發展出許多以電腦輔助設計的軟體工具來組成資料路徑,依據這些軟體的組成原理與設計,它們可以分為分散式 ... 於 ndltd.ncl.edu.tw -

#56.VITO の學習筆記: 如何變更SQL Server 預設的資料檔路徑與 ...

如果你跟我一樣覺得這樣子很麻煩的話,底下的示範就是說明如何變更這個預設目錄的值,讓使用SSMS 時可以方便一點點。 變更預設的「資料檔路徑」. 首先,在 ... 於 vito-note.blogspot.com -

#57.相連結的帳戶與資料夾路徑-Dropbox 說明

相連結的帳戶與資料夾路徑. 如果您是使用Dropbox 桌面應用程式,且已將Dropbox 個人帳戶與Dropbox 團隊帳戶連結,您的電腦上會出現兩個Dropbox 資料夾。 於 help.dropbox.com -

#58.新聞稿-金管會發布「金融科技發展路徑圖」,以3年提升數位 ...

二、 資料共享:加速推動「開放銀行」;建立與第三方服務機構合作資訊揭露制度;訂定金控轄下子公司客戶資料共享之相關機制與規範;訂定金融市場跨 ... 於 www.fsc.gov.tw -

#59.檔案位置選項- 2021 - SOLIDWORKS 說明

列出您可以定義搜尋路徑的檔案類型。 資料夾, 顯示給定檔案類型的搜尋路徑。 加入(A), 加入所選文件類型 ... 於 help.solidworks.com -

#60.如何得知「我的文件」資料夾的實際位置? - 如意網站

在「檔案總管」中,點按「我的文件」,按滑鼠右鍵,點選「內容(R)」。 · 在「目標」頁籤的「目標資料夾位置」即顯示「我的文件」資料夾的實際位置。 於 yes.nctu.edu.tw -

#61.資料存放路徑

1. 概述1.1 版本FineBI 版本功能變動6.0-6.0.9抽取叢集環境下,支援透過節點檔案配置抽取資料存放的絕對路徑。1.2 應用場景抽取資料下, ... 於 help.fanruan.com -

#62.電腦新手教學:我從網路下載的文件存在哪個位置? - Ragic

從瀏覽器下載的資料,要在哪個資料夾找」,跟你的電腦和瀏覽器的設定有關。電腦和瀏覽器通常有一個預設的下載路徑,有需要的話也可以在電腦/瀏覽器的 ... 於 www.ragic.com -

#63.考慮密集資料路徑結構之電路擺置 - Airiti Library華藝線上圖書館

實體設計 ; 資料路徑 ; 電路擺置 ; 規律性萃取 ; 密度模型 ; physical design ; datapath ; placement ; regularity extraction ; density model. 於 www.airitilibrary.com -

#64.變更自訂資料提供者的來源路徑 - SAP Help Portal

針對FHSQL 資料來源使用瀏覽按鈕,可讓您指出任何有效的可用連線。 限制 您無法在4.2 SP3 版本的HTML 介面中,變更Excel 資料提供者的檔案路徑。 於 help.sap.com -

#65.Windows 更改使用者個人資料夾路徑位置設定教學 - KJie Notes

在新買或重灌完成的Windows系統電腦,使用者個人資料夾(例如:『我的文件』、『音樂』和『桌面』等等其他)都會跟系統預設為同個磁碟區C槽。 於 www.kjnotes.com -

#66.冷層中儲存之資料的檔案路徑和結構描述- AWS IoT SiteWise

原始資料會以Apache AVRO ( .avro ) 格式儲存在冷層中。 檔案路徑. AWS IoT SiteWise使用以下範本將設備資料(測量值) 儲存在 ... 於 docs.aws.amazon.com -

#67.【修復】「Windows 無法存取指定的裝置、路徑或檔案」錯誤

EaseUS Data Recovery Wizard可以從Windows 10/8/7電腦救回永久刪除的檔案,當然也包括HDD、SSD、USB、SD卡、外接硬碟...等資料救援。它支援還原刪除照片、影片、音訊、 ... 於 tw.easeus.com -

#68.macOS 指定路徑資料夾如何前往開啟?3 步驟快速學會!

在Windows 系統內,如果想要前往指定路徑資料夾,你只要知道路徑或是複製路徑,隨便開啟一個資料夾或是檔案總管,把路徑貼上就可以前往,但是macOS ... 於 adersaytech.com -

#69.如何變更Visual Studio 專案預設路徑 - Duran 的速寫筆記

我們透過Visual Studio 建立新專案時,系統會預設專案資料在系統磁碟特定位置(不同Visual Studio 版本會預設在不同的位置),若沒有手動變更,久而久之 ... 於 note.duranhsieh.com -

#70.各國颱風路徑| 災防中心資料服務平台

各國颱風路徑. ::: 基本資料. 防救災資料類別. 水文. 上架日期. 2020-10-16. 提供機關. 國家災害防救科技中心. 104. 觀看檔案資料 ... 於 datahub.ncdr.nat.gov.tw -

#71.將Windows 10 如何在標題列顯示完整檔案路徑? |

輕鬆幾個步驟變可以在估工作列上完整呈現檔案的路徑,不妨試試看囉! ①、點選上方箭頭處的『檢視』頁籤,再選擇『選項』。 ... ②、 再選擇資料夾選項中的 ... 於 www.wellife.com.tw -

#72.通行交易查詢 - 遠通電收

... 連結網址,連結至網站閱覽您通行交易明細喔! 提醒您,交易明細為正常收費時段才會有相關紀錄,暫停收費時段,本公司因無收費,故無法申請暫停收費期間之交易資料 ... 於 www.fetc.net.tw -

#73.專題文章:網頁設計中絕對路徑、文件相對路徑和網站根目錄 ...

... 但是,在設計網頁時,於本機端連結時,不需要將連結的文件或目標指定完整的URL,而只是指定目前文件存放位置,或網站根目錄資料夾的相對路徑。 於 www.cadch.com -

#74.Mac 檔案路徑複製教學,一鍵複製Mac 資料夾路徑或檔案路徑!

我們在Mac 上儲存的檔案或資料夾都有它自己的路徑位置,假設我將cat.jpg 這個圖片檔放在Mac 桌面的話,那它的Mac 檔案路徑就是/Users/使用者 ... 於 www.tech-girlz.com -

#75.怎樣自訂快速檔案夾路徑? - T客邦

首先打開檔案總管,點選想要新增的資料夾並按下右鍵,點選快速選單中的【傳送到】→【桌面(建立捷徑)】。 怎樣自訂快速檔案夾路徑? Step 2. 接著到桌面 ... 於 www.techbang.com -

#76.Linux 檔案/目錄/路徑

雖然Linux 沒有如Windows 的C/D/E 碟的概念,但對目錄(資料夾)的觀念是蠻類似的,在Linux 文字界面下的目錄操作,只要搞定〝絕對路徑〞和〝相對路徑〞 ... 於 www.hy-star.com.tw -

#77.端對端資料路徑保護(ETEP) | 穩定性– 宜鼎國際Innodisk

端對端資料路徑保護(End-to-End Data Path Protection, ETEP) 可確保資料在每一個環節的完整性,從資料一進入SSD 開始,直到資料離開SSD。ETEP以錯誤校正碼(Error ... 於 www.innodisk.com -

#78.絕對路徑規格對相對路徑規格 - IBM

在分散式分析模式中,資料檔和指令語法檔案的相對路徑規格是相對於目前伺服器,不是相對於您的本機電腦。如/mydocs/mydata.sav 的相對路徑規格,並不是指向本機磁碟中 ... 於 www.ibm.com -

#79.[知識] iOS 中一些重要路徑

系統相關 · 一般系統App 相關 · 通話記錄CallHistory · iMessage 及簡訊 · Health Kit 資料(備份需加密) · Home Kit 設定 · iCloud Drive · Safari 相關 · Watch ... 於 garynil.tw -

#80.Windows:內建的複製取得「資料夾目錄路徑」或「檔案路徑 ...

Windows:內建的複製取得「資料夾目錄路徑」或「檔案路徑」的幾個方式( 點擊「Ctrl + Shift + C」最快速). 山姆大豬 6月14, 2023. 我常需要把某個目錄或某個檔案的路徑 ... 於 www.unclesampig.com -

#81.使用IOS-XE資料路徑資料包跟蹤功能進行故障排除 - Cisco

本檔案介紹如何透過封包追蹤功能對Cisco IOS-XE®軟體執行資料路徑封包追蹤。 必要條件. 需求. 思科建議您瞭解以下資訊:. 在基於QFP(量子流處理器)的 ... 於 www.cisco.com -

#82.SQL Server 學習筆記: [MySQL]:查詢資料庫的存放路徑datadir

若要查詢MySQL 資料庫的資料存放路徑,可以使用以下的方式:. 示範環境. MySQL Community Server 5.7.17; Windows Server 2016. 預設的資料目錄: 於 sharedderrick.blogspot.com -

#83.熱帶氣旋路徑資訊- 地理信息系統版|香港天文台(HKO)

颱風路徑| 當有熱帶氣旋/颱風進入北緯7至36度,東經100至140度的範圍,或在此範圍內形成,天文台會在兩小時內發放首次的熱帶氣旋/颱風路徑圖。 於 www.hko.gov.hk -

#84.「走讀臺灣・城南尋趣」史博館新打造手遊路徑 - 文化部

藝術散步」手語走讀路徑。在聽人與聾人老師的專業帶領下,讓聽障朋友也能領略南海學園藝術之美。 另外 ... 於 www.moc.gov.tw -

#85.[SQL SERVER]修復Model 資料庫路徑錯誤| RiCo技術農場

如果你改了M:\xxx路徑,這時系統只有D、E、F的話,你無法先透過複製檔案來解決,. 這時可以透過–T3608 防止SQL Server 自動啟動並復原任何資料庫(master ... 於 dotblogs.com.tw -

#86.Matlab 導引:檔案與路徑

My Documents 去(通常在桌面上看到的資料夾名稱是【我的文件夾】)。 >> cd C:\MATLAB\bin >> cd 'C:\My Documents' >> cd C:\My Documents ... 於 bcc16.ncu.edu.tw -

#87.路徑小幫手- pathlib

Python就可以根據你提供的路徑找到你要的檔案。 ... 它是根據你目前執行指令的資料夾地點(Current Working Directory),與所指定的File的相對位置。 於 www.learnwithshin.com -

#88.如何找到系統磁碟區路徑? - QNAP

系統磁碟區通常是NAS中建立的第一個資料磁碟區,除了你的資料之外,還會存儲部分系統檔案。 透過SSH連線QNAP NAS 執行以下指令以取得系統磁碟區的路徑,在這個範例當中 ... 於 www.qnap.com -

#89.各旅次路徑原始資料(M06A) - 政府資料開放平臺

旅次路徑. 相關網址. https://tisvcloud.freeway.gov.tw/history/TDCS/M06A/. 備註. 相關資料集. 交通部高速公路局北區養護工程分局暨所屬單位地址及電話一覽表 ... 於 data.gov.tw -

#90.臺灣2050淨零排放路徑及策略總說明 - 國家發展委員會

我國於2022年3月正式公布「臺灣2050淨零排放路徑及策略總說明」,提供至2050年淨零之軌跡與行動路徑,以促進關鍵領域之技術、研究與創新,引導產業綠色轉型,帶動新一 ... 於 www.ndc.gov.tw -

#91.手動輸入目的地的路徑 - Ricoh

按下[連接測試]。 連接測試用於檢查指定的共用資料夾是否存在。 如果出現 “連接到PC失敗。檢查設定。” 訊息,請參閱疑難排解的「使用掃描器功能時的疑難排解」。 於 support.ricoh.com -

#92.瞭解Dreamweaver 範本中的路徑

因此,請務必將.dwt 檔案保持在Dreamweaver 建立的範本資料夾中。為了避免混淆,「不要」將其他網站元素(影像來源檔案或HTML 文件) 儲存在「範本」資料夾 ... 於 helpx.adobe.com -

#93.影印機掃描到電腦怎麼做?讓你秒變影印機設定達人

1.建立資料夾(影印機掃描後放置於電腦內的路徑). Œ 點選「新增資料夾」→輸入「scan」作為資料夾名稱. 影印機掃描設定-1. 2.設定共用資料夾和使用權限. 於 www.aurora.com.tw -

#94.Windows 10 NAS 路徑架構解析

請注意,系統碟的資料無法在PDM 管理介面檢視,且磁碟機C 沒有使用RAID,建議您初始設定完後可以將資料備份至【磁碟機D 】中。 【磁碟C 】對應【系統碟】 ... 於 blog.ite2nas.com -

#95.Windows 10 資料夾路徑大全(IIS Folder)

Windows 10 資料夾路徑大全(IIS Folder) · IIS 伺服器層級設定檔 · 系統音效Sound Files · Custom Host File to set mappings of IP addresses to host name ... 於 sdwh.dev -

#96.學習路徑- O'Reilly for Higher Education 電子書資料庫

學習路徑介紹. 學習程式語言,發展新技能,或開始獲得全新的知識。每條學習路徑都是 ... 於 proquest.libguides.com