類比ic dcard的問題,我們搜遍了碩博士論文和台灣出版的書籍,推薦楊善國 寫的 應用電子學(第二版)(精裝本) 和劉傳璽,陳進來的 半導體元件物理與製程:理論與實務(四版)都 可以從中找到所需的評價。

另外網站[心得] GG產線帶貨仔轉職類比IC設計 - PTT Brain也說明:PTT | 最近剛從GG產線整合離職且轉職成功,在PTT得到很多面試資訊,故寫下這篇回饋科技版。在GG的工作內容就不贅述,以免整篇負能量太嚴重, ...

這兩本書分別來自全華圖書 和五南所出版 。

國立陽明交通大學 電子研究所 劉建男所指導 郭東杰的 以機器學習輔助之進化演算法 實現考量參數變異的快速類比電路尺寸調整方法 (2021),提出類比ic dcard關鍵因素是什麼,來自於製程變異、類比電路尺寸調整、進化演算法、機器學習。

而第二篇論文國立陽明交通大學 電子研究所 劉建男所指導 周暐翔的 透過部份學習實現彈性佈局遷移的技術 (2021),提出因為有 部分學習、類比電路佈局遷移的重點而找出了 類比ic dcard的解答。

最後網站交大電資四年修課心得則補充:... 大學部選修課程:計算機組織(資工)、作業系統概論(資工)、自動控制系統(電機)、積體電路設計導論(電工)、類比積體電路導論(電機)、數位訊號 ...

應用電子學(第二版)(精裝本)

為了解決類比ic dcard 的問題,作者楊善國 這樣論述:

作者依教學經驗及專業知識,並為兼顧學習內容及學習效果,本書由最基礎的半導體材料及PN接面開始講起,到雙層元件(二極體)、三層元件(電晶體)、四層元件(閘流體)、線性積體電路-OP,到常用的應用電路包括:運算放大器構成之應用電路、電壓調整器、主動濾波器、功率放大器等,使學生可習得電子元件及其構成電路的基礎知識。另修習本科目的學生可能來自不同的專業背景,對電學的觀念及基礎或有所不同,為顧及對電學較生疏學生的需要,特別增加「電學基本概念複習」一章(第零章),使學生具有起碼的電路基礎,以協助學生進入電子電路之領域,並助益往後的教學。 本書特色 1.本書由最基礎的半導體材料及PN接

面開始講起,到雙層元件(二極體)、三層元件(電晶體)、四層元件(閘流體)、線性積體電路-OP,到常用的應用電路,使學生可習得電子元件及其所構成電路的基礎知識。 2.修習本科目的學生可能來自不同的專業背景,對電學的觀念及基礎或有不同,特別增加「電學基本概念複習」,使學生具有基礎的電路概念,以協助學生進入電子電路之領域,並助益往後的教學。 3.本書適用大學、科大機械、自動化科系『應用電子學』、『電子學』課程使用。

以機器學習輔助之進化演算法 實現考量參數變異的快速類比電路尺寸調整方法

為了解決類比ic dcard 的問題,作者郭東杰 這樣論述:

進化演算法被廣泛應用於各種優化問題,因其高準確度和對不同電路的強適應性,相當適合被應用在類比電路尺寸設計上。然而,若在電路尺寸設計中考慮製程變異的影響,將會大量增加電路模擬次數,使其無法被應用於大規模電路上。儘管最近的一些相關研究採用了機器學習技術來加速優化過程,但很少有人在他們的方法中考慮製程變異的影響。在本篇論文中,我們提出了一種應用於類比電路尺寸設計的進化演算法,可以快速地考慮製程變異對良率影響。透過機器學習模型,我們能夠在進行模擬前初步預測新電路樣本的效能好壞,並過濾掉表現可能較差的新電路樣本,節省許多不必要的模擬時間,加快收斂的速度。此外,我們也提出了一種新的類力學模型來引導演算法

優化良率。基於先前過程中的電路樣本,所提出的類力學模型可以預測設計是否具有更好的良率,而無需執行耗時的蒙特卡羅分析。與先前的研究相比,我們所提出的方法顯著減少了進化演算法過程的模擬次數,有助於產生具有高可靠性和低成本的實用設計。相同的概念也可以用在類比電路遷移,大幅縮短改變製程時的尺寸再優化時間。從幾個類比電路的實驗來看,我們的方法確實非常有效率。

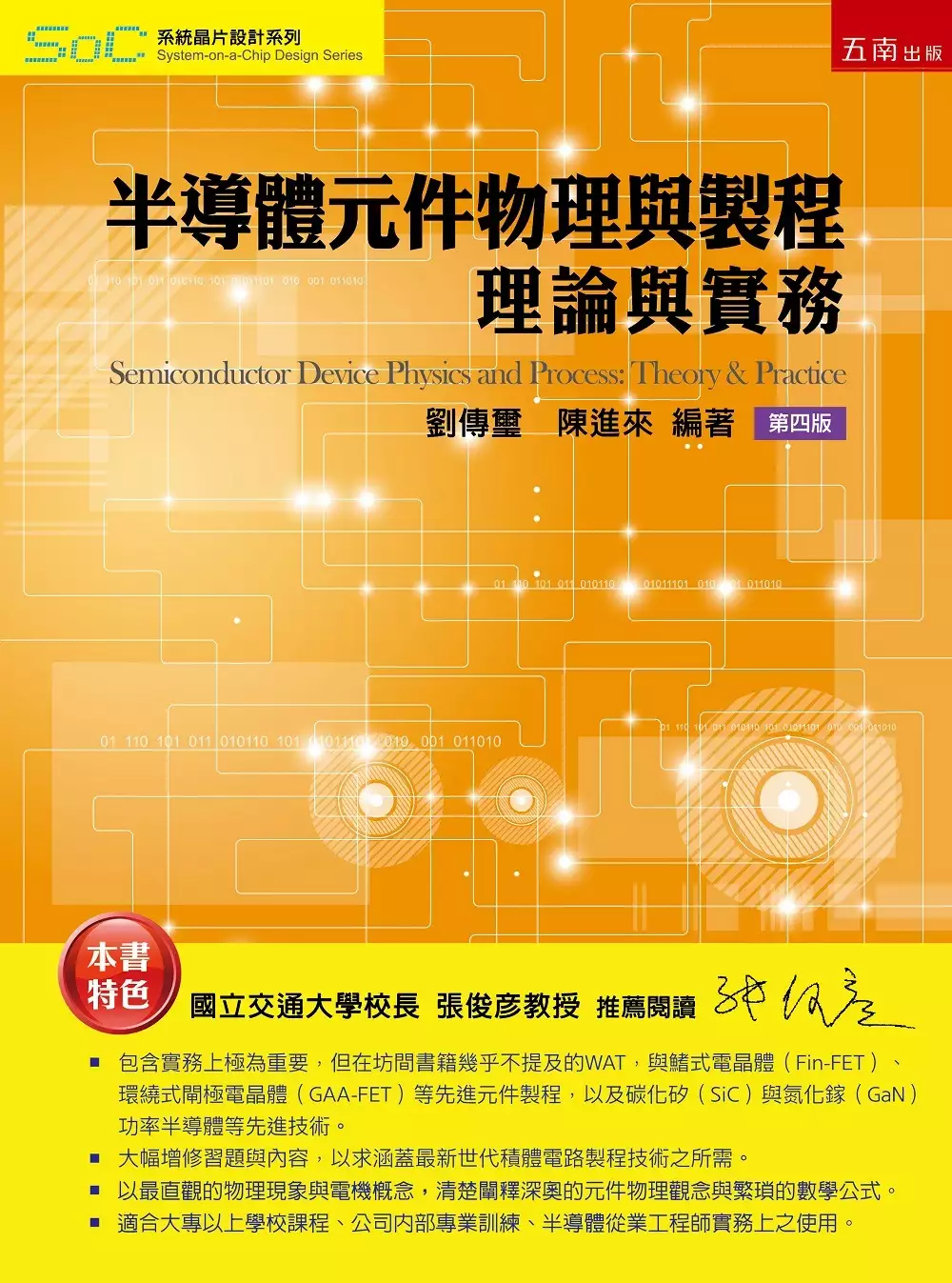

半導體元件物理與製程:理論與實務(四版)

為了解決類比ic dcard 的問題,作者劉傳璽,陳進來 這樣論述:

以深入淺出的方式,系統性地介紹目前主流半導體元件(CMOS)之元件物理與製程整合所必須具備的基礎理論、重要觀念與方法、以及先進製造技術。內容可分為三個主軸:第一至第四章涵蓋目前主流半導體元件必備之元件物理觀念、第五至第八章探討現代與先進的CMOS IC之製造流程與技術、第九至第十二章則討論以CMOS元件為主的IC設計和相關半導體製程與應用。由於強調觀念與實用並重,因此儘量避免深奧的物理與繁瑣的數學;但對於重要的觀念或關鍵技術均會清楚地交代,並盡可能以直觀的解釋來幫助讀者理解與想像,以期收事半功倍之效。 本書宗旨主要是提供讀者在積體電路製造工程上的know-how與know-wh

y;並在此基礎上,進一步地介紹最新半導體元件的物理原理與其製程技術。它除了可作為電機電子工程、系統工程、應用物理與材料工程領域的大學部高年級學生或研究生的教材,也可以作為半導體業界工程師的重要參考 本書特色 ●包含實務上極為重要,但在坊間書籍幾乎不提及的WAT,與鰭式電晶體(Fin-FET)、環繞式閘極電晶體(GAA-FET)等先進元件製程,以及碳化矽(SiC)與氮化鎵(GaN)功率半導體等先進技術。 ●大幅增修習題與內容,以求涵蓋最新世代積體電路製程技術之所需。 ●以最直觀的物理現象與電機概念,清楚闡釋深奧的元件物理觀念與繁瑣的數學公式。 ●適合大專以上學

校課程、公司內部專業訓練、半導體從業工程師實務上之使用。

透過部份學習實現彈性佈局遷移的技術

為了解決類比ic dcard 的問題,作者周暐翔 這樣論述:

在現今先進製程技術中,越來越多的寄生效應需要被考慮,尤其是在設計敏感的類比電路。由於傳統類比電路設計自動化工具的不成熟,類比電路佈局還是仰賴耗時的人工設計。在類比佈局合成方法中,佈局遷移(Layout migration)是一種可以保留設計師佈局知識的方法,這個技術能根據原始電路佈局的拓樸,在不同的電晶體尺寸或是不同的製程下產生新的佈局。雖然佈局遷移能夠有效地保留原本佈局的考量,但此技術只能應用在具有同架構的設計。為了改善傳統佈局遷移的靈活性,本論文提出一個部分學習的佈局遷移流程。在這篇論文中,我們沒有直接遷移完整的佈局,而是僅從舊設計中提取建構塊(Build block)的佈局模板,由於數

據庫中的建構塊可以從不同的設計提取而來,我們的方法可以支援不同架構的設計且維持設計師的佈局知識。最後,因為問題大小已經在塊級別(Block-level)下大幅縮小,新設計的佈局可以在很晚的時間內透過組合建構塊完成。根據實驗結果,本論文提出的方法可以保持良好的電路性能且盡可能保持設計師的佈局知識。

想知道類比ic dcard更多一定要看下面主題

類比ic dcard的網路口碑排行榜

-

#1.Ic 設計工作內容

確保IC設計各路電路或其他零件安裝方式、及產品功能不衝突. 依照顧客或公司開出之需求單作產品IC設計. 設計研發中所欲之上次介紹完了類比ic工程師相信 ... 於 les-rencontres-crisalide.fr -

#2.【招生】徵大二暑假專題實習(詳見本頁底)

IC 設計課程 ... 郭教授具國內外工業界與學校卓越的研究及教學經驗(教授榮譽、教育部及台灣半導體中心獲獎),在類比/混合訊號積體電路的研究已有三十多年,博碩士學生 ... 於 msic.ee.ncku.edu.tw -

#3.[心得] GG產線帶貨仔轉職類比IC設計 - PTT Brain

PTT | 最近剛從GG產線整合離職且轉職成功,在PTT得到很多面試資訊,故寫下這篇回饋科技版。在GG的工作內容就不贅述,以免整篇負能量太嚴重, ... 於 www.pttbrain.com -

#4.交大電資四年修課心得

... 大學部選修課程:計算機組織(資工)、作業系統概論(資工)、自動控制系統(電機)、積體電路設計導論(電工)、類比積體電路導論(電機)、數位訊號 ... 於 ilewu.medium.com -

#5.類比數位選擇- 科技業板 - Dcard

想詢問板上各位前輩,聽說想去做數位的話,只要修課就可以了,目前按照我本人的計畫的話,預計四下結束可以把數位相關的課都修完(參考聯發數位學程) ... 於 www.dcard.tw -

#6.詢問台北類比IC設計公司- 科技業板 - Dcard

大家好~,小弟目前在園區某上櫃薪資排名前幾名的IC設計公司擔任類比電路設計工程師,由於家裡因素因此未來換工作想往台北發展,目前看到就矽創、昇 ... 於 www.dcard.tw -

#7.Ic 設計公司ptt

因此想請問一下各位前輩們台北的類比IC設計公司選項有哪些比較推薦? ... IC設計請益- 研究所板| Dcard. 台灣的IC設計公司通常都是沒有自設工廠的 ... 於 congresomagnetobiologia.es -

#8.電腦包dcard推薦!最新限時優惠中- Pinkoi

床包dcard 年6月9日—之前都買幾百塊的床包,睡起來不會覺得不舒服, … ... 聯發科表示,今年招募重點職缺包含軟韌體開發、數位IC設計、類比IC設計、射頻IC設計、通訊 ... 於 luqofom.aprosmoto.cz -

#9.奇景- H_類比IC設計工程師- 科技業板 - Dcard

如題,小弟有幸收到面試邀約,想請問各位年薪百萬的學長姐們面試大約會問什麼問題呢?謝謝!,PS 已爬文- 類比,設計,工程師,面試,求職. 於 www.dcard.tw -

#10.奕力ptt

公司立錡科技奕力科技職稱類比IC工程師類比IC工程師內容MB(mobile) TP(touch部· 奕力: 系統工程師到公司後會先做 ... 奕力面試請益- 科技業板| Dcard. 於 motivplus-formations.fr -

#11.類比ic 設計工程師 - Puzzlout

Phison Electronics Corp_群聯電子股份有限公司面試心得| 面試趣. 類比ic 設計工程師. Offer請益(類比ic設計工程師) - 科技業板| Dcard. W Fixed Gain ... 於 puzzlout.fr -

#12.類比 - Dcard

第一份工作就百萬年薪類比IC工程師 · 博士班生涯一覽(供參考) · 坊間流傳~含金量最高!!類比晶片設計 · 110台大電子乙(類比ICS組)正取心得 · 還是喜歡類比儀表板 · 有人有修過 ... 於 www.dcard.tw -

#13.成大類比ic ptt :: 博碩士論文下載網

博碩士論文下載網,類比好難,混合訊號IC PTT,110 成大微電子PTT,類比電路工程師PTT,成大微電子教授,轉數位IC PTT,類比數位IC,成大微電子dcard. 於 thesis.imobile01.com -

#14.Q&A專區 - 元智大學電機工程學系(甲組)

另外、電子工程領域最主要可以學到數位及類比IC設計相關的知識及技術,透過晶片 ... 系系學會IG粉專,不定時會提供各種活動資訊給大家,也可以從Dcard上找到一些資訊。 於 eea.ee.yzu.edu.tw -

#15.坊間流傳~含金量最高!!類比晶片設計- 科技業板 - Dcard

設計流程類比系統電路設計的開發流程是遵守全客製化開發流程英文為full-custom design flow ... 課程類比IC 的電路主題大致有下面幾個(排除RF IC ). 於 www.dcard.tw -

#16.Ic 設計公司ptt

[請益] 類比IC設計真的找不到好工作嗎? - Tech_Job - MYPTT ... 詢問台北類比IC設計公司- 科技業板| Dcard. 我表弟沒有ptt帳號,我幫他代po 研所畢業 ... 於 bienhetreenforet74.fr -

#17.類比IC真的很難學嗎- 研究所板 - Dcard

前陣子去找類比的教授談他說類比只適合少數真的對電子學、電路有興趣的人沒興趣只是為了薪資建議別來三年畢業是基本且要很認真否則可能四年甚至畢不了 ... 於 www.dcard.tw -

#18.rfic/類比ic - 科技業板 - Dcard

rfic/類比ic. 科技業. 2月16日04:56 (已編輯). 各位前輩們好,小妹我是電機系通訊組的學生,如果以下問題有冒犯之處請見諒 虛線以下是我的 ... 於 www.dcard.tw -

#19.Ic 設計工作內容 - AgenceTximeleta

帶您基本認識晶片究竟是如何生成? /4/8- 個工作機會|IC設計工程師【矽誠科技股份有限公司】、類比IC設計工程師【茂彰光電股份 ... 於 agencetximeleta.fr -

#20.PTT、Dcard推薦!女孩們的保養小心機『大研生醫淨密樂蔓越 ...

在這裡幫大家彙整出ptt/dcard 6款高cp值家用平價電腦椅、電競電腦椅推薦, ... 聯發科表示,今年招募重點職缺包含軟韌體開發、數位IC設計、類比IC設計、射頻IC設計、 ... 於 ehayohovum.metaclimate.exchange -

#21.類比ic工作ptt的推薦與評價 - 最新趨勢觀測站

關於類比ic工作ptt 在[請益] 類比IC設計真的找不到好工作嗎? - Tech_Job - My PTT 的評價; 關於類比ic工作ptt 在第一份工作就百萬年薪類比IC工程師- 科技業板| Dcard 的 ... 於 news.mediatagtw.com -

#22.IC設計種類?EDA? - 工作板 - Dcard

最近在逛104,發現IC設計有好多種,數位IC、類比IC、射頻IC,甚至有的只寫IC設計,想請問這幾種到底有什麼不同呢?另外,EDA是屬於數位還是類比呢? 於 www.dcard.tw -

#23.[討論] 如果碩班讀元件想要走類比有機會嗎? PTT推薦- Tech_Job

wumingxian 07/23 17:15只會類比"模擬"就想設計類比IC?? 超英趕美了! ... dlija7814 07/23 19:01建議去dcard問比較有答案,這邊一堆看到光電就反射. 於 pttyes.com -

#24.[討論] 如果碩班讀元件想要走類比有機會嗎? - Tech_Job板

只會類比"模擬"就想設計類比IC?? ... 推dlija7814: 建議去dcard問比較有答案,這邊一堆看到光電就反射性崩潰的,根本得不到什麼有用的資訊43F 07/23 ... 於 disp.cc -

#25.鍾勇輝Yung-Hui Chung - 電子工程系

實驗室, 混合訊號IC實驗室(EE601-2). 研究領域, 類比/混合訊號積體電路設計、類比/數位轉換電路(ADC/DAC)、數位校正(Digital Calibration)電路、生醫感測電路(IA)與 ... 於 www.et.ntust.edu.tw -

#26.[不刪文] 類比IC 碩班新生修課規劃,修數位or 專注碩論? - Dcard

[不刪文] 類比IC 碩班新生修課規劃,修數位or 專注碩論? 研究所. 5月28日22:20. 各位學長姊們好, 第一次在板上發文,一路上也看過很多學長姊們有關類比修課回文,但 ... 於 www.dcard.tw -

#27.【設計|類比ic anog|ic|al】職缺- 2023年6月熱門工作機會

想找更多的設計|類比ic anog|ic|al相關職缺工作,就快上1111人力銀行搜尋。 ... 帶領Dcard Visual Design Team 共同創造獨特且創新的視覺體驗,並引導團隊成員的職 ... 於 www.1111.com.tw -

#28.半導體業年終最高不是台積電! 這家每位工程師都超過200萬

這兩天Dcard有網友以「台積開獎」為題,請大家分享台積電今年分紅狀況。 ... 台灣半導體業前五名高薪職務依序為類比IC設計工程師136.6萬元、數位IC ... 於 tw.tech.yahoo.com -

#29.華邦104

華邦| Dcard ... 華邦路竹廠- 科技業板| Dcard. 「在華邦這個大家庭,我們鼓勵 ... 職務類別:數位IC設計工程師、類比IC設計工程師、IC佈局工程師。 於 labattmobile.fr -

#30.類比ic - Le Mecano Des Soufflants

數位積體電路可以包含任何东西, · 類比IC(Analog IC)是電子裝置的重要零件,從消費電子、電腦、通信、 ... 類比IC真的很難學嗎- 研究所板| Dcard. 於 lemecanodessoufflants.fr -

#31.第一份工作就百萬年薪類比IC工程師- 科技業板 - Dcard

YT 版,網誌好讀版,早安我是彼得先生,今天要來分享我的工作-類比IC工程師,一份起薪就是百萬的夢想職業,半導體製造是台灣的驕傲(TSMC), ... 於 www.dcard.tw -

#32.ICS組專任教師 - NTU GIEE|國立臺灣大學電子工程學研究所

高電能效率(低功率/高速)類比及混合信號積體電路設計資料轉換器積體電路IC設計電能擷取電源轉換器積體電路IC設計太空晶片設計硬體安全的密鑰晶片設計. 於 giee.ntu.edu.tw -

#33.類比IC面試分享- 科技業板 - Dcard

1.外商M 工作內容:HD相關,類比IP設計面試內容:純英文面試,問你履歷上做過的所有project,你在裡面扮演的角色、規格、如何設計、layout plane …等等, ... 於 www.dcard.tw -

#34.不要再問幾趴可推到四大了,電子系42%推到台大電子類比正取五

【111台大電子乙(類比ICS)正取5心得】 研究所3月20日00:21 北科電子,系排42%,大學專題做電源管理IC,題目為Buck Converter with Current Mode ... 於 www.dcard.tw -

#35.Re: [情報] IC設計開始結構調薪 - PTT評價

滷肉結構調薪- Dcard 是不是滷肉啊看這漲幅應該有30% 以下是節錄: ... 類比ic設計工程師連三線豬屎屋新人底薪都不止這價了更不要提二線一線有年資的 ... 於 ptt.reviews -

#36.類比IC

想看更多文章分享?或是想找特定資訊? 下載Dcard 看網友真實討論! 用App 查看完整內容. 於 www.dcard.tw -

#37.ICS走類比的各位有後悔過嗎- 科技業板 - Dcard

我還在思考要走數位還是類比,數位對我來說比較好上手,可是就是有一大堆人在競爭,類比門檻高,比較少人跨的進來,不過養成是真的有難度,有聽過學長 ... 於 www.dcard.tw -

#38.類比ic與數位ic的選擇- 研究所板 - Dcard

我目前是電機系大三生,專題做的是有關ai的數位ic,將來會想要推ic設計的研究所,但目前成績大概最高是推上中字輩的,上網查過類比ic跟數位ic設計都各 ... 於 www.dcard.tw -

#39.做類比IC到底怎樣才是一個合格的論文- 研究所板 - Dcard

最近在尋找研究方向上一直很無助,覺得做某方面主題的power ic 的架構大概都那樣,幾個控制block改來改去,如果說要創新的話我肯定是要想一個全新的 ... 於 www.dcard.tw -

#40.數位、類比IC 教授選擇- 研究所板 - Dcard

目前上了某間ICS,熱門兩年數位的都搶完了,有寄信給一個類比數位都做的教授但說只剩類比一個名額,爬文大概2.5年畢業好像也不操,數位還沒寄信但應該 ... 於 www.dcard.tw -

#41.數位IC讓資工系來做是不是會比電機系好很多? - Dcard

總覺得電機學了一堆東西到數位IC基本上就用不太到了,什麼工程數學/電磁學/電子學後段,有點偏掉,反倒是資工系,有著程式思維,還有計算機組織/作業 ... 於 www.dcard.tw -

#42.有沒有大神能幫類比寫一篇QQ - 科技業板 - Dcard

數位ic,課程推薦,做愛. 於 www.dcard.tw -

#43.「模擬類比IC電路」在職進修、線上學習 - 104求職精靈

還有Facebook、Google Ads、LINE Ads、Dcard Ads 廣告建立和設定,還能了解#自動化行銷和應用策略! 我們還會教你粉專經營、論壇經營和社群分析,以及如何用手機拍攝出超有 ... 於 nabi.104.com.tw -

#44.關於類比或數位ic - 研究所板 - Dcard

關於類比或數位ic. 研究所. 2021年6月10日06:31. 目前碩班是讀固態方面的因未來的工作似乎也只能去台積電,好幾位學長都撐不下去了,所以目前想重考,但目前還沒決定 ... 於 www.dcard.tw -

#45.類比IC的未來? - 科技業板 - Dcard

當初數位類比都推最後數位沒上只好來類比經過一學期研究覺得類比的世界好複雜好奇妙現在有點做不太下去有類比IC的前輩願意說說以後去職場的情況嗎? 於 www.dcard.tw -

#46.類比IC設計工程師- 聯發科技集團_立錡科技股份有限公司 - 比薪水

有想要錢就進來拼吧,... 有升遷管道. 固定加薪. 公司制度完善. 於 salary.tw -

#47.類比

下學期的三門IC課程心得分享. PTT的使用者很少,可是Dcard很難被google到,所以發在PTT再搬運過來. ... [不刪文] 類比IC 碩班新生修課規劃,修數位or 專注碩論? 於 www.dcard.tw -

#48.映智科技股份有限公司面試心得

映智科技股份有限公司面試經驗、面試問題、自我介紹、面試準備、面試流程、薪水年終等精彩內容都在面試趣。最新面試:類比ic工程師面試、類比ic工程師面試。 於 interview.tw -

#49.類比IC轉職分享- 科技業板 - Dcard

面試也告一段落,整理一下面試過程消個業障,目前在某廠當類比IC工程師負責的部分為ADC 工作內容還算輕鬆,沒事還能打打期貨。雖然這半年空單薛了一筆 ... 於 www.dcard.tw -

#50.數位ic與類比ic 工作比較- 科技業板 - Dcard

不好意思打擾各位,想請各位年薪百萬的工程師們,可以留下自己的工作資料~,數位or類比/公司/年資/工時/待遇,相信很多人會因為你的留言收穫滿滿, ... 於 www.dcard.tw -

#51.為何年均薪超過150 萬的IC 設計工程師只收電機 - CakeResume

同時,電機系出路相當多元,但是以「硬體工程師」為主,往IC、半導體、通訊等產業 ... 體電路元件、微電子工程;還有電路設計組,研究類比電路設計、數位積體電路等。 於 www.cakeresume.com -

#52.交大電子乙b教授dcard :: 藥局地圖

然後碩士期間多修數位ic的課,2.轉職做類比,找類比的教授,不過要3年-實驗室,研究所....交大電子乙B教授(我保證不刪).心情58・留言73.,2021年11月6日—最近推甄 ... 於 drugstore.moreptt.com -

#53.有關類比IC以及數位IC啊- 研究所板 - Dcard

其實我一直有個疑惑,常聽大家說類比缺<<數位缺,但為什麼學校一堆類比老師,數位的反而還比類比少很多. ... 有關類比IC以及數位IC啊. 於 www.dcard.tw -

#54.Tech_Job - [請益] 類比IC讀博是否值得 - MYPTT

各位前輩好, 小弟是四大的碩班學生,目前主要是做ADC/DAC相關的題目, 前陣子剛下出去第一顆IC,對於整個從設計、layout到整合的過程也不會感到厭倦, 最近在教授的 ... 於 myptt.cc -

#55.立錡_ 類比IC設計(資深)工程師(PMIC)面試請益- 科技業板 - Dcard

如題,小弟我是113混血電類碩,最近收到立錡的類比IC面試,工作內容如下:問題來了,我碩論是做RFIC ,跟類比佔不上邊,唯一勉強算類比電路的只有一 ... 於 www.dcard.tw -

#56.Ic 設計工作內容 - ALTERNATIF BULLDOG CLUB FRANCAIS

電腦輔助設計工程師| JOBs維基| JOBsMining職涯大數據. 設計研發中所欲之上次介紹完了類比ic工程師相信大家對ic設計的工作內容有一些基礎性的認識 ... 於 alternatifbulldogclubfrancais.fr -

#57.車用類比ic概念股2023-在Facebook/IG/Youtube上的焦點新聞 ...

車用類比ic概念股在2023的熱門內容就在年度社群熱搜話題焦點新聞網. ... 車用類比ic概念股-臉書推薦/討論/評價在PTT、Dcard、IG整理一次看. 於 year.gotokeyword.com -

#58.類比IC設計01 - YouTube

版權所有:台灣大學。李致毅教授轉自。李P講電路https://www.youtube.com/channel/UCYsxNo5PM2jeEWiQGpSGEUA. 於 www.youtube.com -

#59.類比ic有好公司嗎? - 科技業板 - Dcard

如題,一線ic MmNPRS基本上都是數位IC,雖然他們好像也有招類比人才,但是產品都是數位的,類比的發展應該不會比較好,那台灣有類比特別強的公司嗎? 於 www.dcard.tw -

#60.Ic 設計公司ptt

聽懂「一線廠」 - 科技業板| Dcard. 瑞鼎科技營收快速提升,年成長% ,成長幅度達前十名之最,排名從第六名上升至第五名詢問台北類比IC設計公司科技 ... 於 ainpourtous.fr -

#61.茂達電子股份有限公司類比IC設計工程師面試經驗2021.6.29

面試地區:新竹市。相關職務工作經驗:5 年。面試時間:2018 年9 月。面試結果:沒通知。面試過程:第一次面試: 面試有筆試先寫兩張考卷之後兩位主管 ... 於 www.goodjob.life -

#62.奕力ptt - pharmacie clemenceau

研替面試心得(奕力/群聯/揚智/松翰/台灣類比科) - 工作板| Dcard ... 公司立錡科技奕力科技職稱類比IC工程師類比IC工程師內容MB(mobile) TP(touch部· ... 於 pharmacieclemenceaulalonde.fr -

#63.類比IC設計快畢業正要找工作,但挺徬徨的的. - 科技業板 - Dcard

類比IC 設計快畢業正要找工作,但挺徬徨的的. ... 也有聽到去年大徵才今年凍結的事情其實還挺擔心可能明年收到兵單自己都還不知道找不找得到工作. 類比. 於 www.dcard.tw -

#64.四中碩做類比ic設計- 科技業板 - Dcard

小弟今年考上四中資工所的硬體組,做數位的教授都被找完了只剩下類比的,請問如果四中碩畢有辦法找到類比ic設計的工作嗎?因為網路上都說要純血四大才 ... 於 www.dcard.tw -

#65.Ic 設計工作內容 - Riviera playa

Ic設計到底要會什麼,在做什麼? - 科技業板| Dcard. 設計研發中所欲之上次介紹完了類比ic工程師相信大家對ic設計的工作內容有一些基礎性的認識數位ic ... 於 rivieraplaya.fr -

#66.類比vs數位- 研究所板 - Dcard

大家好,小弟目前考上中字輩Ics,想請問大家,類比是存搞電子學,數位是除了verilog還要會演算法跟phython嗎?因為實在不太喜歡打程式如果只是verilog ... 於 www.dcard.tw -

#67.中正偉文研究所轉學考補習班- 台大ICS乙組(類比)正取...

台大ICS乙組(類比)正取https://www.dcard.tw/f/graduate_school/p/233452317. 於 m.facebook.com